# A FAST AND SCALABLE FEEDBACK-DRIVEN SCHEDULER FOR DATACENTER APPLICATIONS

## Mayco Souza Berghetti

Advisor: Prof. Ronaldo Alves Ferreira, Ph.D.

Co-advisor: Prof. Fabrício Barbosa de Carvalho, D.Sc.

College of Computing Federal University of Mato Grosso do Sul 2025

# A FAST AND SCALABLE FEEDBACK-DRIVEN SCHEDULER FOR DATACENTER APPLICATIONS

## Mayco Souza Berghetti

#### Master's Thesis

Advisor: Prof. Ronaldo Alves Ferreira, Ph.D.

Co-advisor: Prof. Fabrício Barbosa de Carvalho, D.Sc. o

College of Computing

Federal University of Mato Grosso do Sul

2025

## Abstract

Microsecond-scale datacenter applications demand strict latency guarantees while operating under high load and variable service times. This environment often involves a mix of extremely short and long requests, where short requests—lasting just a few microseconds—are frequently delayed by longer ones due to Head-of-Line (HOL) blocking, leading to higher latencies, especially at the tail. However, existing approaches to mitigate HOL blocking, such as centralized dispatching, fine-grained preemption, and resource reservation, face fundamental scalability limitations. This work introduces Synergy, a cooperative, application-aware scheduling system that uses direct feedback from applications to prioritize short requests, dynamically adapts scheduling parameters, and avoids unnecessary preemptions. Synergy adopts a decentralized architecture with distributed queues, job-aware preemption, and dynamic quantum sizing. By eliminating centralized classification and using real-time application measurements, Synergy effectively mitigates HOL blocking without compromising throughput. Synergy outperforms state-of-the-art systems, achieving up to 43% higher throughput while meeting microsecond-scale service-level objectives.

**Keywords**: datacenter, head-of-line blocking, user-level scheduler.

| "The important thing is not to stop questioning |

|-------------------------------------------------|

| Curiosity has its own reason for existing."     |

| — Albert Einstein                               |

| ii                                              |

|                                                 |

## Agradecimentos

Dedico este trabalho à minha mãe do coração, Carolina Berghetti. Suas palavras de encorajamento, sempre presentes nos momentos mais desafiadores, foram fundamentais para que eu seguisse em frente com coragem e determinação.

Agradeço, com profundo carinho, à minha esposa, Nadia Tatiane dos Santos Ojeda, ao meu irmão, Marlon Souza Berghetti, e à minha mãe, Marinete Souza da Silva Berghetti. O apoio e o incentivo constante de vocês foram essenciais para a realização desta etapa tão importante da minha vida. Sou sinceramente grato por estarem ao meu lado em cada passo desta jornada.

Minha sincera gratidão ao Professor Ronaldo Alves Ferreira, meu orientador, por sua dedicação, paciência e comprometimento ao longo desta jornada acadêmica. Suas orientações e ensinamentos foram de valor inestimável, contribuindo significativamente para meu crescimento pessoal e profissional. Graças ao seu apoio, tive a honra de apresentar parte do nosso trabalho no Simpósio Brasileiro de Redes de Computadores e Sistemas Distribuídos (SBRC) em 2024, uma experiência enriquecedora e marcante. Sou imensamente grato por sua confiança, disponibilidade e por ser uma fonte de inspiração.

Agradeço profundamente ao Fabrício Barbosa de Carvalho por ter me acompanhado ao longo desta jornada. Sua orientação atenta, generosidade ao compartilhar conhecimentos e constante incentivo foram fundamentais para o desenvolvimento deste trabalho. Sua colaboração teve um impacto significativo no meu crescimento técnico e acadêmico ao longo do processo.

Estendo também meu agradecimento ao amigo Maximilian Jaderson de Melo, cuja paciência e disposição em compartilhar seu conhecimento foram essenciais nos primeiros passos desta caminhada. Sua ajuda inicial fez toda a diferença e sou profundamente grato por isso.

Expresso minha sincera gratidão aos professores Luciano Paschoal Gaspary (UFRGS), Nahri Balesdent Moreano (UFMS) e Carlos Alberto da Silva (UFMS) por gentilmente aceitarem integrar minha banca examinadora e pelas valiosas contribuições oferecidas, as quais foram fundamentais para o aprimoramento desta dissertação.

Por fim, agradeço ao Instituto Federal de Mato Grosso do Sul (IFMS) pelo suporte institucional e pelas condições oferecidas ao longo desta jornada acadêmica.

Agradeço também à Universidade Federal de Mato Grosso do Sul (UFMS) pela valiosa oportunidade de formação, pelos recursos disponibilizados e pelo ambiente propício ao desenvolvimento deste trabalho.

## Acknowledgements

I dedicate this work to my heart mother, Carolina Berghetti. Your words of encouragement, always present during the most challenging moments, were essential in helping me move forward with courage and determination.

I express my deep affection and gratitude to my wife, Nadia Tatiane dos Santos Ojeda, my brother, Marlon Souza Berghetti, and my mother, Marinete Souza da Silva Berghetti. Your unwavering support and constant encouragement were crucial to the completion of this important chapter in my life. I am truly grateful for having you by my side every step of the way.

My sincere gratitude goes to Professor Ronaldo Alves Ferreira, my advisor, for his dedication, patience, and commitment throughout this academic journey. His guidance and teachings were of immeasurable value, contributing significantly to my personal and professional growth. Thanks to his support, I had the honor of presenting part of our work at the Brazilian Symposium on Computer Networks and Distributed Systems (SBRC) in 2024—an enriching and memorable experience. I am deeply thankful for his trust, availability, and for being a constant source of inspiration.

I am also deeply grateful to Fabrício Barbosa de Carvalho for accompanying me throughout this journey. His attentive guidance, generosity in sharing knowledge, and continuous encouragement were fundamental to the development of this work. His collaboration had a significant impact on my technical and academic growth throughout the process.

I would also like to extend my thanks to my friend Maximilian Jaderson de Melo, whose patience and willingness to share his knowledge were essential in the early stages of this journey. His initial support made all the difference, and I am profoundly thankful for it.

I express my sincere gratitude to Professors Luciano Paschoal Gaspary (UFRGS), Nahri Balesdent Moreano (UFMS), and Carlos Alberto da Silva (UFMS) for kindly agreeing to serve on my examination committee and for their valuable contributions, which were fundamental to the improvement of this dissertation.

Finally, I am grateful to the Federal Institute of Mato Grosso do Sul (IFMS) for the institutional support and the conditions provided throughout this academic journey. I also thank the Federal University of Mato Grosso do Sul (UFMS) for the

valuable educational opportunity, the resources made available, and the academic environment that enabled the development of this work.

## List of Acronyms

**API** Application Programming Interface

APIC Advanced Programmable Interrupt Controller

**c-FCFS** Centralized First Come First Serve

CI Compiler Interrupts

CPU Central Processing Unit

**d-FCFS** Descentralized First Come First Serve

**DARC** Dynamic Application-aware Reserved Cores

**DMA** Direct Memory Access

**DPDK** Data Plane Development Kit

DRAM Dynamic Random-Access MemoryEAL Environment Abstraction Layer

FCFS First Come First Serve HOL Blocking Head-of-Line Blocking

I/O Input/OutputIP Internet Protocol

**IPC** Inter-Processor Communication

IPI Inter-Processor Interrupts

JBSQ Join-Bounded-Shortest-Queue

JIQ Join-Idle-Queue

JSQ Join-Shortest-Queue

kRPS Thousand Request per Second

LLC Last-Level Cache

LLVM Low Level Virtual Machine

MRPS Million Request per Second

MSR Model Specific Register

NAPI New API

NIC Network Interface Card

NUMA Non-Uniform Memory Access

PCI Peripheral Component InterconnectPOSIX Portable Operating System Interface

PS Processor SharingRTC Run-to-CompletionRTT Round-Trip Time

**SLO** Service-Level Objective

SR-IOV Single Root I/O VirtualizationTCP Transmission Control Protocol

TID Thread Identifier

TLS Thread-Local StorageUDP User Datagram Protocol

**UINTR** User Interrupts

**UITT** User-Interrupt Target Table

**UPID** User Posted-Interrupt Descriptor

VF Virtual Function

## List of Algorithms

| 5.1 | Aplication Pseudocode     | 39 |

|-----|---------------------------|----|

| 5.2 | Synergy Request Selection | 40 |

| 5.3 | Timer Core                | 43 |

## List of Figures

| 2.1 | Kernel-based vs. Kernel-bypass packet processing                   | 6  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Request distribution strategies                                    | 8  |

| 2.3 | Load balancing strategies                                          | 10 |

| 4.1 | Simulation of different overheads to centralized dispatching       | 31 |

| 4.2 | HOL Blocking mitigation strategies                                 | 32 |

| 5.1 | Synergy overview                                                   | 37 |

| 5.2 | Request life cycle                                                 | 38 |

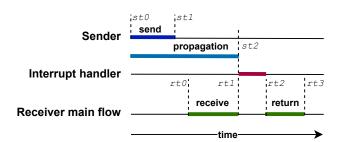

| 5.3 | Interrupt delivery path stages                                     | 48 |

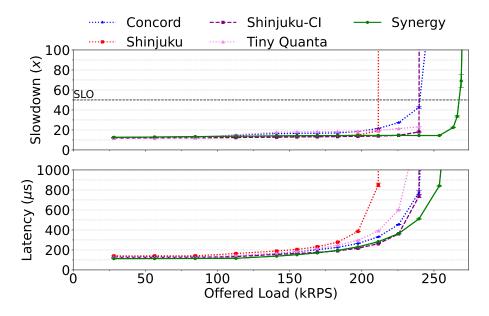

| 6.1 | Results to High workload                                           | 53 |

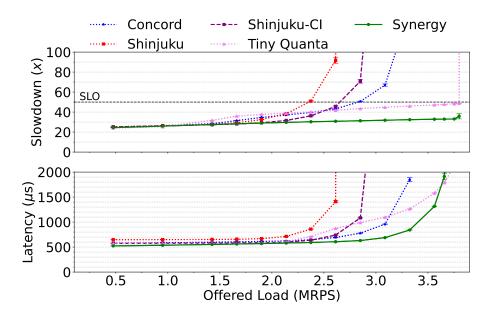

| 6.2 | Results to Extrene workload                                        | 55 |

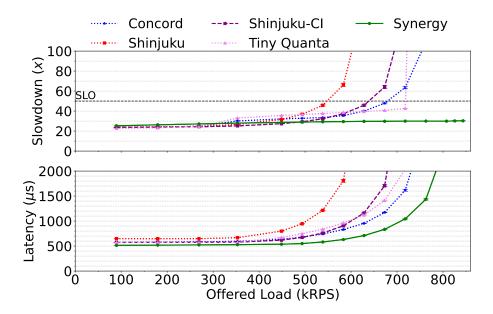

| 6.3 | Results to ZippyDB workload                                        | 56 |

| 6.4 | Results to levelDB application                                     | 57 |

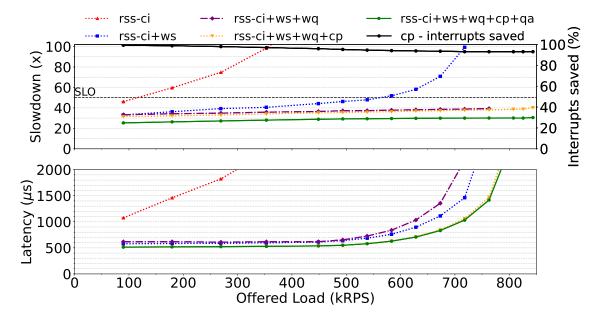

| 6.5 | Breakdown of Synergy's performance improvements                    | 58 |

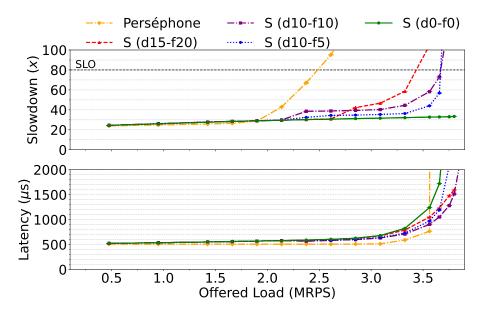

| 6.6 | Synergy's knobs for adjusting request processing priorities        | 61 |

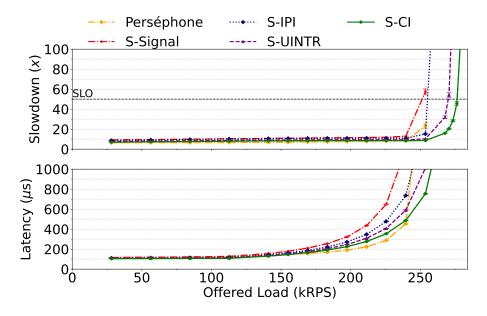

| 6.7 | Synergy's performance using different interrupt methods            | 62 |

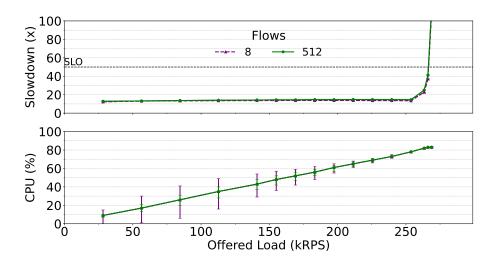

| 6.8 | Synergy's performance with uneven flow distribution across cores . | 63 |

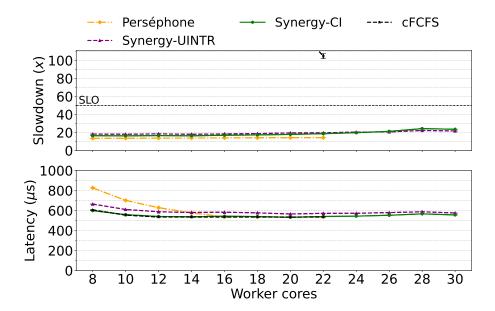

| 6.9 | Synergy multicore scaling capacity                                 | 65 |

## List of Tables

| 4.1 | Design space comparison                  | 35 |

|-----|------------------------------------------|----|

| 5.1 | Overhead for different interrupt methods | 49 |

| 6.1 | Evaluated workloads                      | 51 |

## Contents

| 1        | Introduction |                                            |    |  |

|----------|--------------|--------------------------------------------|----|--|

|          | 1.1          | Main Contributions                         | 3  |  |

|          | 1.2          | Thesis Organization                        | 5  |  |

| <b>2</b> | Bac          | ekground                                   | 6  |  |

|          | 2.1          | Kernel and Kernel-Bypass Packet Processing | 6  |  |

|          | 2.2          | Request Distribution                       | 8  |  |

|          | 2.3          | Load Balance Management                    | 9  |  |

|          | 2.4          | Task Scheduling Models                     | 11 |  |

| 3        | Rel          | ated Work                                  | 15 |  |

|          | 3.1          | Network Protocol Stack                     | 15 |  |

|          | 3.2          | System Interference                        | 19 |  |

|          | 3.3          | Head-of-line Blocking                      | 24 |  |

| 4        | Des          | sign Space                                 | 29 |  |

|          | 4.1          | Motivation                                 | 29 |  |

|          | 4.2          | Request Dispatching and Load Balancing     | 30 |  |

|          | 4.3          | HOL-Blocking Mitigation                    | 32 |  |

|          | 4.4          | Application Awareness                      | 33 |  |

|          | 4 5          | Extra Core and Ontimizations               | 34 |  |

| 5       | Syn        | ERGY                                         | 36         |

|---------|------------|----------------------------------------------|------------|

|         | 5.1        | Design                                       | 36         |

|         | 5.2        | Implementation                               | 45         |

| 6       | Evaluation |                                              |            |

|         | 6.1        | Methodology and Setup                        | 50         |

|         | 6.2        | Synergy vs. Preemptive Systems               | 52         |

|         | 6.3        | Ablation Study                               | 57         |

|         | 6.4        | Multicore Scaling                            | 64         |

| 7       | Disc       | cussion                                      | 66         |

|         | 7.1        | Delegating Classification to the Application | 66         |

|         | 7.2        | Timeliness and Practical Implementation      | 67         |

|         | 7.3        | Benefits of Application Feedback             | 68         |

|         | 7.4        | Dealing with Multiple Request Types          | 69         |

| 8       | Con        | clusion                                      | 70         |

|         | 8.1        | Future Work                                  | 71         |

| Bi      | bliog      | graphy                                       | <b>7</b> 3 |

| ${f A}$ | Pub        | olications                                   | 82         |

## Chapter 1

### Introduction

Datacenter applications, such as real-time analytics, online gaming, and social networks, demand response times at microsecond scales to meet strict service-level objectives (SLOs) [70]. These applications are composed of complex, latency-sensitive workflows where every microsecond matters [71]. The challenge lies not only in processing large numbers of concurrent requests but also in ensuring that even the slightest delays are minimized [1, 19, 29].

At microsecond timescales, traditional software architectures struggle to keep up with the demands of high-throughput, low-latency workloads. Processing delays are compounded by factors such as contention for CPU cores [50], memory bandwidth [25], and sudden bursts of requests that introduce queuing and scheduling inefficiencies [19,62]. To make matters worse, datacenter workloads often exhibit service times with high dispersion, where a mix of extremely short and long requests must coexist [12, 20, 29, 33, 36, 45, 53]. Short requests, taking just a few microseconds, are often delayed by longer ones—an issue known as *Head-of-Line* (HOL) Blocking—leading to higher latencies, especially at the tail [19,62].

To address the HOL Blocking problem and bound tail latency, recent research has explored kernel-bypass systems with a variety of scheduling strategies [7, 25, 30, 34, 35, 50, 53, 55, 70], including employing centralized dispatchers for load balancing [20,

36, 51], preempting long requests to prioritize short ones [30, 33, 36, 45, 69], and intra-server resource reservation [20, 21, 51]. Unfortunately, these approaches often scale poorly and force servers to run at low utilization (e.g., below 40%) to meet strict SLOs [5].

Each of these strategies faces fundamental limitations that reduce their effectiveness at scale. Centralized dispatchers [20, 33, 36, 50], despite effectively distributing load, become bottlenecks under high load, which limits throughput and causes servers to remain underutilized. Fine-grained preemptive schedulers [33, 36, 69] introduce substantial overhead due to indiscriminate context switching and interrupt handling. Even optimized variants [33, 45] struggle with workloads exhibiting high service time variance, leading to poor cache performance and increased CPU costs. Resource reservation strategies [20] further rely on external classifiers to distinguish request types, which adds redundant classification effort and often leads to incorrect predictions when service times depend on dynamic application states. This situation calls for more nuanced, workload-aware scheduling approaches.

In datacenters, where enterprises have full control over the application stack—including the application, operating system, kernel-bypass system, and application scheduler—there is significant potential to design more cooperative and effective scheduling mechanisms. This control can provide the scheduler with rich application-level knowledge—such as request types, service times, and workload patterns—so it can make more informed and fine-grained decisions. Additionally, the scheduler can incorporate real-time feedback from the application and measurement data to adjust scheduling parameters dynamically, allowing it to better meet strict SLOs, reduce tail latencies, and improve overall resource utilization.

#### 1.1 Main Contributions

This work introduces Synergy, a system designed to work in close cooperation with applications to scale efficiently on multicore architectures while addressing the fundamental limitations of existing systems. By leveraging direct application feedback, Synergy enables differentiated treatment of requests based on their expected service times, allowing it to prioritize short requests and mitigate HOL Blocking without compromising throughput or scalability. Synergy combines decentralized scheduling—where requests are distributed across multiple queues and scheduled independently—with dynamic load balancing and job-aware preemption to meet microsecond-scale SLOs even under high-load, high-variance conditions typical of datacenter workloads.

Specifically, Synergy adopts a decentralized dispatcher, where the NIC (Network Interface Card) distributes requests across multiple queues, each mapped to a dedicated worker. To handle load imbalances, Synergy employs work stealing [55], allowing underutilized workers to pull requests from overloaded ones and dynamically rebalance the load. This mechanism ensures efficient resource utilization [46] while preserving the benefits of decentralized dispatching. By eliminating the need for a centralized dispatcher—a well-known source of contention in prior systems [20, 33, 36, 50]—Synergy avoids a critical bottleneck.

In Synergy, applications classify requests and provide feedback to the scheduler, enabling differentiated handling of short and long requests. Short requests run to completion without interruption to minimize latency. Long requests, by contrast, can be preempted and resumed later to avoid delaying others and mitigate HOL blocking. Preempted requests are placed in a common wait queue rather than being reinserted into the original worker's queue, which allows them to be redistributed more effectively across workers than with queue-length-based strategies, such as work stealing alone. This strategy ensures that long requests do

not accumulate unevenly and that idle workers can resume deferred computation, improving overall responsiveness and resource utilization.

In addition to scheduling decisions, Synergy uses application feedback to compute the scheduling quantum dynamically based on the service times of the requests and operator-defined parameters. This design eliminates the drawbacks of a large fixed quantum, which can unnecessarily delay short requests [35, 36, 45], and offers flexibility to prioritize different request types. Also, Synergy employs job- and load-aware conditional preemption instead of time-based preemption. This approach avoids unnecessary context switches when a worker queue is empty, which minimizes overhead and improves overall performance.

Finally, by delegating request classification to the application, SYNERGY eliminates the need for a centralized classifier [20] and supports more flexible and accurate classification. This approach accounts for scenarios where service times depend not only on the request type but also on factors such as the specific operations pipelined within a request [58] or the popularity of a search term [18].

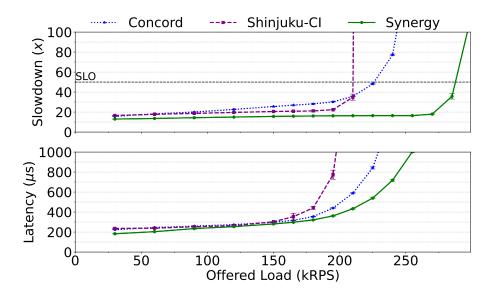

We implement SYNERGY as a libOS using DPDKDPDK to bypass the Linux kernel and compare it with Shinjuku [36], Perséphone [20], Concord [33], and Tiny Quanta [45], which use different techniques to mitigate HOL blocking. Through application-aware design and several optimizations, SYNERGY significantly improves throughput while meeting microsecond-scale latency SLOs. For example, in the Extreme workload (§6.2), SYNERGY increases throughput by 24–43% over prior systems and effectively mitigates HOL blocking up to 81% system load. We also perform a comprehensive evaluation of SYNERGY's internal mechanisms and behavior under diverse conditions. This evaluation includes an ablation study, sensitivity experiments with varying configuration parameters, tests under load imbalance, and evaluations of scalability with an increasing number of cores. The source code of SYNERGY and the scripts for reproducing our results are available at https://github.com/Synergy-repo/synergy.

### 1.2 Thesis Organization

The remainder of this work is organized as follows. Chapter 2 introduces foundational concepts necessary to fully understand the work. Chapter 3 reviews the most relevant related work. Chapter 4 analyzes the design space explored by previous systems and presents the motivation behind the proposal developed in Chapter 5. Chapter 6 evaluates the proposed approach in comparison to existing solutions. Chapter 7 explores practical considerations and potential applications of the proposed feedback technique and provides a summary of its benefits. Finally, Chapter 8 summarizes the main contributions and concludes the thesis.

## Chapter 2

## Background

This chapter briefly overviews the background material necessary to understand the contributions of this work. Section 2.1 introduces packet processing in general-purpose operating systems, such as Linux, and presents techniques that improve processing speed. Section 2.2 describes request distribution strategies. Section 2.3 explains how to manage load balancing effectively. Finally, Section 2.4 examines different task scheduling models.

#### 2.1 Kernel and Kernel-Bypass Packet Processing

Figure 2.1: Kernel-based vs. Kernel-bypass packet processing.

The interval between the arrival of data at the NIC (Network Interface Card) and its consumption by the application involves several processing steps [10, 40, 68]. General-purpose operating systems like Linux typically use an interrupt-driven model for network processing. As illustrated in Figure 2.1a, when a packet arrives,

the NIC transfers it to main memory via DMA (*Direct Memory Access*) and raises an interrupt to notify the CPU. The operating system (OS) then processes the packet through the protocol stack. OS places the data in the reception queue of the corresponding socket based on the flow identified in the packet header. When the application performs a system call such as recv, the OS copies the packet data from kernel space to a user-space buffer.

Modern versions of Linux introduce optimizations to improve packet processing, including interrupt coalescence and NAPI (New API) [40]. With interrupt coalescence, the NIC intentionally delays interrupt generation to batch multiple incoming packets, thereby reducing interrupt overhead during high traffic. However, this batching introduces additional latency for the earliest packets in the batch.

NAPI replaces the purely interrupt-driven model with a hybrid approach that combines interrupts and polling. During high traffic, the system turns off interrupts and relies on a dedicated CPU core to periodically poll the NIC's receive queue and retrieve packets. This polling strategy improves performance and reduces interrupt handling overhead, although it may waste CPU cycles when traffic is low.

Instead of relying on the traditional kernel-based packet processing model, many high-performance networking systems adopt a technique known as kernel bypass, which allows user-space applications to interact directly with hardware (e.g., the NIC) [7, 20, 25, 33, 36, 38, 45, 50, 53, 55], as illustrated in Figure 2.1b. These systems rely on frameworks such as DPDK [31], Netmap [59], and technologies like SR-IOV (Single Root I/O Virtualization) [53] to bypass the kernel and implement custom user-level network protocol stacks, thereby enabling low-latency and high-throughput network I/O.

By moving many traditionally kernel-level functions into user space, these systems reduce context switches, eliminate data copying between kernel and user memory, and give applications tighter control over scheduling and resource allocation. Additionally, full network polling is commonly employed in

high-performance kernel-bypass systems, improving latency and throughput compared to conventional kernel-based packet processing. For example, Shenango [50] improves CPU efficiency for many co-located latency-sensitive and batch applications by combining user-level networking with user-level thread scheduling. Kernel bypass systems work particularly well for microsecond-scale applications commonly found in modern datacenters, where even small delays in packet handling can significantly impact overall latency and system responsiveness.

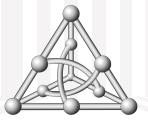

#### 2.2 Request Distribution

Request distribution strategies fall into two broad categories: centralized and decentralized models. In the centralized model, the system places all incoming requests into a single queue and assigns a dedicated core to dispatch these requests to available workers. Several systems adopt the centralized model by dedicating a core to perform request distribution between workers [20, 36, 51], as illustrated in Figure 2.2a. Although centralized dispatching offers better load balancing in theory [67], it suffers from scalability constraints in practice, particularly due to contention and synchronization overhead [46].

Figure 2.2: Request distribution strategies.

In contrast, the decentralized model distributes incoming requests across multiple queues. While this approach introduces additional complexity in maintaining load balance, it significantly improves scalability by reducing contention and increasing parallelism. Many systems implement the decentralized model by exploiting

hardware features available in modern Network Interface Cards (NICs) to implement decentralized dispatching, as depicted in Figure 2.2b. Examples include Receive Side Scaling (RSS) [61] and Intel Flow Director [52] mechanisms, both of which distribute network packets across multiple receive queues in the NIC. Recent high-performance I/O frameworks [7, 25, 55] widely adopt these mechanisms.

In the case of RSS, the NIC determines packet distribution by computing a hash over selected packet header fields, e.g., 5-tuple of the packet. Rather than directly selecting a queue using the hash, the NIC uses it as an index into an indirection table stored in hardware. This indirection table maps hash values to receive queues, allowing flexible assignment of flows and enabling multiple distinct flows to share the same queue. Some systems dynamically adjust the indirection table at runtime to mitigate imbalances resulting from uneven flow distribution [3, 13–15].

#### 2.3 Load Balance Management

Balancing the workload between workers ensures more efficient utilization of available resources, improves overall throughput, and reduces request latency. Various load-balancing policies can be employed to achieve this goal. Some rely on real-time knowledge of the system state, while others operate with minimal or no system awareness. These strategies generally reflect a trade-off between scalability and balance quality: the more precise the load distribution, the more overhead the system incurs, which can hinder scalability.

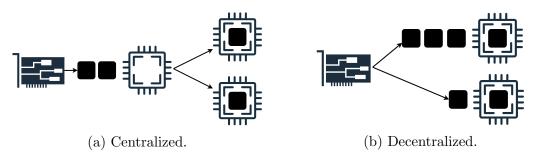

We now discuss the principal load balancing strategies that are most relevant to this work:

• Join-Idle-Queue (JIQ), illustrated in Figure 2.3a, assigns incoming requests exclusively to idle workers. It achieves efficient load distribution with minimal overhead under moderate load, but it depends on tracking real-time worker availability. Although JIQ distributes load effectively, it scales poorly because

Figure 2.3: Load balancing strategies.

it must continuously track which workers are idle.

- Join-Bounded-Shortest-Queue (JBSQ), illustrated in Figure 2.3b, dispatches requests to any worker whose queue length is below a predefined threshold. Compared to JIQ, JBSQ reduces scalability limitations while offering a moderate load balance. Like JIQ, JBSQ implementations typically rely on a centralized dispatcher.

- Join-Shortest-Queue (JSQ), illustrated in Figure 2.3b, dispatches requests to one of the workers with the fewest tasks in their queue. By relaxing the precision of load information, JSQ improves scalability relative to JIQ and JBSQ at the cost of slightly less optimal load distribution.

- Work-stealing, illustrated in Figure 2.3c, makes idle workers steal tasks from busier workers to balance the workload between workers. This technique avoids centralized coordination and scales well, although it generally yields less optimal load balance than centralized methods.

Overall, these policies reflect a fundamental trade-off: centralized strategies like JIQ and JBSQ can provide better load balance but suffer from limited scalability, while JSQ offers a middle ground by trading some balance precision for improved scalability. Decentralized approaches like work-stealing prioritize scalability further, at the cost of even less precise load distribution.

#### 2.4 Task Scheduling Models

Task processing often follows the First-Come-First-Served (FCFS) model, where workers execute tasks in a run-to-completion (RTC) manner, strictly respecting their arrival order. When systems combine this execution model with centralized or decentralized request dispatching, they implement the scheduling policies known as c-FCFS and d-FCFS, respectively. Another widely used execution model is Processor Sharing (PS), in which each task runs for a fixed time slice (or quantum) before yielding the processor to allow another task to execute. According to queueing theory, FCFS performs best in workloads with low variability in processing times, whereas PS offers better performance under workloads characterized by high variability or heavy-tailed distributions [67].

To implement PS, systems must interrupt tasks frequently. Generally-purpose operating systems typically involve configuring hardware timers, such as the Advanced Programmable Interrupt Controller (APIC), to generate periodic interrupts. For instance, before executing a task, the system programs the APIC to trigger an interrupt after a specific time interval. Upon receiving the interrupt, the scheduler can preempt the current task and switch to another if needed.

In contrast to traditional kernel-level scheduling, several recent systems move scheduling decisions to user space [25, 30, 33, 36, 42, 50, 56], aiming to avoid the costly context switches associated with transitions between user and kernel modes. User-level schedulers can operate cooperatively, where the application developer manually inserts yield points in the code. Examples of libraries supporting this cooperative model include GNU Portable Threads [26], C++ coroutines [16], and Windows fibers [48]. Alternatively, user-level scheduling can be preemptive, which requires mechanisms capable of interrupting the currently running task.

Currently, the available mechanisms to support preemption in user space include: POSIX signals [9, 63], user-level interrupts [30, 42], and, compiler-based

interrupts [33, 45]. The following sections expand on the discussion of these alternatives.

#### 2.4.1 Signals

POSIX-compliant systems use signals as the primary mechanism for event signaling and asynchronous communication in user space. Programs can generate signals programmatically (e.g., via alarm) or explicitly send them between threads or processes (e.g., using tgkill), which makes signals a viable tool for implementing user-space task preemption [9,63].

Although POSIX signals offer a standardized and flexible interface for handling asynchronous events, they introduce considerable overhead, especially in latency-sensitive or high-frequency preemption scenarios. Much of this overhead stems from the need to transition between user and kernel modes. When a thread receives a signal, the kernel interrupts its execution, saves the processor state, and invokes a user-defined signal handler. Once the handler completes, the kernel must restore the thread's previous context, typically by issuing a signeturn system call to resume execution at the point of interruption. Additionally, when delivering a signal to a process, the kernel must select an appropriate thread as the recipient, a process that may require inter-core communication and incur further scheduling overhead.

#### 2.4.2 User Interrupts

User Interrupts (Uintr) [64] are a recent hardware mechanism that enables user-space applications to send and receive interrupts without kernel involvement, eliminating system call overhead. Intel's Sapphire Rapids processors support this feature through a set of Model Specific Registers (MSRs), as described below.

To receive user interrupts, an interrupt vector must be written to the UINV

register, allowing the processor to differentiate user interrupts from other types. When a user interrupt occurs, the processor transfers control to a user-space handler, which the system must preconfigure in the IA32\_UINTR\_HANDLER register. Each thread that can receive user interrupts maintains a User Posted-Interrupt Descriptor (UPID), pointed to by the IA32\_UINTR\_PD register. The UPID structure holds key information, such as the processor APIC ID that the thread is currently running.

To send user interrupts, software uses the SENDUIPI instruction, a new unprivileged instruction that triggers an interrupt to a designated user-level target. Each logical processor that can send user interrupts maintains a User-Interrupt Target Table (UITT), whose base address is stored in the IA32\_UINTR\_TT register. Each UITT entry corresponds to a receive thread and contains a pointer to the UPID structure of the target thread. When the SENDUIPI instruction is executed with a given index, the processor looks up the corresponding UITT entry, retrieves the UPID of the target, and delivers the interrupt using the local APIC to the target's logical processor. The receiving thread will then handle the interrupt using the handler address stored in IA32\_UINTR\_HANDLER.

By enabling fully user-space interrupt handling, Uintr removes system call overhead and achieves performance gains of up to 17.3× compared to traditional asynchronous Inter-Process Communication (IPC) methods [64]. This efficiency has motivated several recent research efforts that explore the use of Uintr in low-latency user-level systems [2, 30, 35, 42].

#### 2.4.3 Compiler Interrupts

Compiler Interrupts (CI) implement a preemption mechanism based on compile-time instrumentation, where the compiler injects checks into the application code to determine whether the currently running task should yield the CPU. The compiler strategically places these yield checks (e.q., at function boundaries), and the

application evaluates them during execution to decide whether a context switch should occur. Consequently, the frequency of context switching directly depends on how often the program includes these yield points.

One of the main advantages of CI is its low context-switching overhead. Unlike asynchronous preemption methods, such as signals, that require the system to save the full processor state, CI yields control with minimal state saving, entirely in user space. This design enables high efficiency in systems that require fine-grained task switching while avoiding the latency and complexity of system calls or signal handling.

Despite these advantages, CI introduces runtime overhead due to the inserted yield checks. When placed too frequently, especially within performance-critical sections such as tight loops, these checks can degrade performance significantly. For example, developers of the Go programming language reported performance slowdowns of up to 95% when applying aggressive instrumentation [27]. Therefore, effective use of CI requires balancing preemption granularity and system performance by carefully selecting where to place yield points, ideally avoiding the critical execution paths.

## Chapter 3

### Related Work

This chapter reviews the most relevant research related to this work. Section 3.1 presents works that specialize in the network protocol stack. Section 3.2 presents works that address different types of interference within a server. Finally, Section 3.3 covers works that tackle the problem of Head-of-Line (HOL) blocking. We defer the comparison of existing approaches with our's to Chapter 4.

#### 3.1 Network Protocol Stack

The protocol stack forms a fundamental component of any network packet processing system. General-purpose operating systems typically implement the stack within the kernel. This design enhances security by isolating applications and simplifies networked software development. However, it also introduces significant processing overhead. Several factors contribute to this overhead, including frequent transitions between user and kernel modes, extensive security checks, and the reliance on large, generic data structures to manage connection state. Furthermore, kernel stacks support a broad range of TCP use cases, which reduce cache efficiency and introduce complex, multi-layered control flows that stall the processor pipeline.

To mitigate these performance bottlenecks, many high-performance systems

bypass the kernel entirely. They use virtualization technologies such as SR-IOV [65] or user-space frameworks like DPDK [31] to access the NIC directly and implement custom protocol stacks in user space. Although these approaches offer substantial performance gains, they often sacrifice security and generality in favor of speed [53].

This section examines systems that optimize the protocol stack to improve network application performance, exploring trade-offs between throughput, latency, and safety.

#### 3.1.1 Arrakis

Arrakis [53] is an operating system designed to minimize the overhead along the application data path by leveraging hardware virtualization technologies. Traditional applications that rely on the Linux kernel and the POSIX socket API often suffer from performance limitations due to overhead introduced by kernel components, such as the protocol stack, scheduling, and packet copying. These factors prevent applications from fully utilizing the underlying hardware capabilities in terms of both throughput and latency.

To address this, Arrakis removes the kernel from the application's data path and delegates it to the role of a control plane responsible for ensuring isolation and security across applications. Arrakis bypasses the kernel during packet processing and eliminates costs associated with kernel scheduling, context switching, and system calls. Furthermore, implementing the protocol stack in user space enables a streamlined and efficient version that significantly reduces processing overhead. In practice, Arrakis achieves up to a 4× reduction in time spent within the protocol stack compared to Linux.

Arrakis employs SR-IOV [65], a technology originally developed to reduce virtualization overhead. SR-IOV allows the creation of virtual functions (VFs) on compatible network devices, with each VF appearing as a distinct PCI device that

can be independently assigned, typically to virtual machines. This direct hardware access eliminates the need for device emulation by a hypervisor. The hypervisor configures the physical NIC, including creating and managing VFs and setting up filters for packet (de)multiplexing between virtual entities.

In the context of Arrakis, the system repurposes SR-IOV to assign virtual functions directly to applications instead of virtual machines. The NIC performs packet demultiplexing and delivers packets directly to the corresponding application queues. Arrakis provides two socket interfaces: a standard POSIX-compatible API and a more efficient native interface. The native interface avoids copying packets between the user and kernel space, enabling higher performance.

Compared to Linux, Arrakis reduces total packet processing time by up to 8.8× using the native socket API and by 2.3× using the POSIX API. For real-world workloads, such as Memcached [47], Arrakis delivers up to a 1.7× throughput improvement. The system also demonstrates near-linear scalability with increasing core counts, up to six cores. Beyond this threshold, performance begins to degrade due to background processes managed by Barrelfish [4], the research operating system on which Arrakis is built.

#### 3.1.2 mTCP

mTCP [34] introduces a user-level TCP/IP protocol stack designed for scalability on multicore systems, with a focus on ease of use and implementation. To achieve high scalability, mTCP applies several optimization techniques, including batch processing of packets and events, using lightweight, per-core data structures that avoid sharing between cores, and enforcing stream affinity per core to reduce synchronization overhead.

mTCP builds upon the PacketShader I/O engine [28] to enable direct access to the NIC from user space, extending it with a new event-driven API tailored for

high-performance networking. It also provides a drop-in replacement for applications using the POSIX socket API by offering analogous functions—e.g., accept becomes mtcp\_accept. For asynchronous event handling, it includes interfaces such as mtcp\_epoll.

The mTCP stack runs as a dedicated thread pinned to the same core as the application thread. Although this architecture introduces some context-switching overhead, mTCP mitigates the impact through lock-free data structures and batching mechanisms that amortize processing costs across multiple events.

One of the core challenges addressed by mTCP is scaling the handling of large numbers of short-lived TCP connections. The Linux kernel suffers from several bottlenecks in such scenarios. For instance, when a socket queue is shared by multiple application threads, it introduces contention. Similarly, the global file descriptor space causes contention, as the kernel must locate the lowest available file descriptor during socket creation (e.g., via the accept syscall), which becomes a bottleneck under high concurrency. Additionally, large data structures such as sk\_buff introduce memory and cache inefficiencies when handling high packet rates.

Thanks to its architectural design and optimizations, mTCP achieves near-linear scalability regarding the number of CPU cores. Moreover, porting applications to mTCP is relatively straightforward: only a small number of code changes are required for programs already using the POSIX socket API—for example, adapting lighttpd required modifying only 65 lines of code. Performance evaluations show that mTCP improves TCP throughput by up to 3.2× compared to the Linux kernel.

#### 3.1.3 TAS

TAS [38] accelerates TCP packet processing for datacenter applications by separating the handling of common and uncommon cases. TAS processes the common case, which includes in-order packet delivery, no fragmentation, and rare

retransmissions, on a fast path. The system delegates exceptional conditions, such as timeouts or out-of-order packets, to a slow path. TAS design uses the observation that most TCP traffic in datacenter environments follows a predictable and optimized pattern.

TAS consists of three main components that communicate via shared memory: the fast path, the slow path, and the protocol stack. The system implements the fast and slow paths as user-space processes pinned to dedicated CPU cores, each running in a separate thread. This architectural separation enables TAS to scale independently of the application workload. TAS exposes the protocol stack as a user-space library compatible with the POSIX socket interface, allowing unmodified applications to interact seamlessly.

TAS achieves high performance and low latency by isolating common-case processing in the fast path and bypassing the kernel through direct NIC access. The system also preserves key properties such as application-level isolation and scalability. Experimental evaluations show that TAS handles many concurrent TCP connections with minimal throughput degradation. Furthermore, TAS improves the tail latency of a key-value store application by  $2.3 \times 2.3 \times 2.3$

#### 3.2 System Interference

Interference in a computer system occurs when some element of the system limits the performance of an application. This section covers systems that address different types of interference.

#### 3.2.1 Arachne

Arachne [56] is a general-purpose user-space thread manager designed to deliver low latency and high throughput for applications that handle short-lived threads.

Many datacenter applications, such as Memcached [47], process requests with service times under 10  $\mu$ s. In such scenarios, the high cost of thread creation in traditional systems, for example, C++ std::thread incurs a creation overhead of approximately 13.3  $\mu$ s [56], makes per-request thread creation infeasible.

To mitigate this, applications typically use thread pools that initialize a fixed number of threads at startup to handle incoming requests. However, when the application spawns more threads than available cores to it, thread multiplexing causes contention and increases latency.

Arachne addresses these challenges by assigning exclusive core usage to applications over longer periods (tens of milliseconds) and dynamically allocating cores based on workload demands. Applications scale their internal parallelism according to the number of assigned cores. In addition, Arachne implements an efficient threading model that supports very short thread lifetimes on the order of microseconds while delivering performance comparable to hand-written event-driven code and preserving the simplicity of thread-based programming.

Arachne consists of three core components:

- Core Arbiter: A dedicated process that runs independently from Arachne applications. It manages core allocation among competing applications based on requests made through the Arachne runtime. Importantly, it does not forcibly revoke cores but uses a priority-based scheme to distribute resources fairly.

- Arachne Runtime: A lightweight thread library used by applications. It efficiently manages threads and handles load balancing by assigning new threads to underutilized cores at creation time.

- Core Policy: Allows each application to define how it will use its allocated cores. For example, an application may reserve a dedicated core for a specific thread (e.g., a dispatcher), while distributing other threads across remaining

cores.

Experimental results show that Arachne improves the 99th percentile latency of Memcached by up to  $40\times$  compared to Linux. These gains stem from exclusive core usage, which reduces interference from other applications, and Arachne's lightweight thread management with minimal load-balancing overhead. When co-deployed with a compute-intensive workload (e.g., the x264 video encoder), Arachne maintains Memcached's low latency.

Similar to systems like Arrakis [53], IX [7], and Shenango [50], Arachne seeks to combine low latency with efficient resource usage. However, unlike those systems, it does not rely on kernel-bypass mechanisms or direct NIC access. This design choice makes Arachne suitable for networked applications and general-purpose workloads requiring responsive, high-throughput threading on multicore systems.

#### 3.2.2 Shenango

Shenango [50] is a system designed to reconcile efficient CPU utilization with the stringent latency requirements of network applications with tail latency Service-Level Objectives (SLOs) in the microsecond range. Unlike traditional systems that adjust core allocations at millisecond intervals [56], Shenango operates at a much finer granularity, making decisions every 5  $\mu$ s. Shenango also uses 5  $\mu$ s of queuing delay as an early congestion signal to determine when to allocate additional CPU cores to an application.

Shenango is composed of two main components: the IOKernel and the runtime. The IOKernel runs on a dedicated core and manages network I/O for applications. Shenango also executes a congestion detection algorithm determining when applications require additional computational resources. The runtime and application code communicate with the IOKernel via shared memory. Shenango provides a user-space protocol stack and thread management system, including

user-level thread scheduling and work-stealing for load balancing across cores.

Using Shenango, applications configure two CPU core allocations: guaranteed and burst cores. The system exclusively reserves guaranteed cores, ensuring a minimum level of performance that it cannot revoke. In contrast, the IOKernel dynamically allocates burst cores based on detected congestion and can reclaim them anytime. The runtime may also voluntarily return idle guaranteed cores to the IOKernel to improve overall CPU utilization.

Shenango's architecture allows it to efficiently serve a mix of workloads, including both batch-processing applications and latency-sensitive services, without sacrificing performance. Its responsiveness and flexible resource management enable better utilization of modern multicore systems, particularly in datacenter environments.

#### 3.2.3 Caladan

Caladan [25] is a system designed to mitigate application interference while improving resource utilization. It builds upon Shenango [50] but introduces several key enhancements. In addition to queuing delay, which Shenango already uses, Caladan incorporates additional signals to detect load changes and interference.

One of Caladan's core innovations is its direct path mode, which bypasses the IOKernel's packet dispatching. This allows application runtimes to communicate directly with the NIC using the libibverbs [43] library, reducing processing overhead. Caladan also includes a custom kernel module called KSCHED, which implements more efficient scheduling mechanisms than the Linux kernel API (e.g., sched\_setaffinity). This module also collects performance counters from remote cores, including cache miss rates.

At deployment, applications receive two categories of CPU cores: guaranteed cores, which the application always has access to, and burst cores, which the system temporarily assigns based on load. Applications fall into Latency-Critical (LC)

and Best-Effort (BE). BE applications operate at a lower priority and only use burst cores. The system can revoke burst cores from BE applications to reduce interference or meet the demands of LC applications. Although LC applications avoid preemption by BE tasks, they can voluntarily release idle cores when load-balancing mechanisms, based on work stealing, fail to find new work.

Caladan uses queuing delay to identify when an application needs more cores. Once a need is detected, it considers both the application's classification (LC or BE) and additional interference signals to make allocation decisions. These signals include request processing time, DRAM bandwidth usage (DRAM BW), and last-level cache (LLC) miss rate.

The first metric helps manage hyper-thread interference by tracking how long a request runs on a core. If the runtime exceeds a defined threshold, the system asks the sibling hyper-thread to yield, idling the core. We use DRAM BW and LLC miss rate in combination to avoid DRAM channel saturation, which can increase memory access latency. When DRAM usage exceeds a set threshold, the system identifies the core with the highest LLC miss rate and revokes that core from the BE task, causing interference. This process continues until DRAM bandwidth usage drops below the limit.

Compared to Parties [17], a previous system designed to mitigate interference, Caladan shows similar performance under constant interference. However, it significantly outperforms Parties when interference is bursty (e.g., due to garbage collection in BE applications). Caladan also achieves comparable latency to other kernel-bypass systems [50,55], and delivers a throughput of 10 million requests per second. Due to its single-queue dispatch design, this is double that of its predecessor, Shenango, which is limited to 5 million requests per second.

## 3.3 Head-of-line Blocking

Head-of-line (HOL) blocking occurs when long-lived requests delay short-lived ones because the latter gets queued behind the former. This section discusses systems that specifically target this issue.

#### 3.3.1 Shinjuku

Shinjuku [36] leverages hardware virtualization features to implement a user-space scheduling system capable of preemption at the microsecond scale. Its goal is to enable fair sharing of CPU resources across requests, preventing long-running operations from blocking short ones. It is crucial in applications with diverse service time distributions. For instance, get/set requests in key-value stores like Memcached [47] typically follow an exponential distribution with low variance, but background tasks (e.g., garbage collection) can introduce long tails. Search engines often exhibit heavy-tailed request distributions such as log-normal, Zipf, or Pareto, while key-value databases like RocksDB [60] experience bimodal distributions, mixing fast operations (e.g., get/put) with slower ones (e.g., range scans).

Shinjuku extends Dune [6], a kernel module that exposes Intel Virtualization Technology (VT-x) features, to support Inter-Processor Interrupts (IPIs) used in preemption. The IPI handling path is heavily optimized, reducing overhead to 1993 cycles, an improvement of 2.1× over the unoptimized 4219-cycle path. Context switching is also enhanced by modifying the Linux ucontext library, reducing the cost from 2290 to just 109 cycles.

Shinjuku implements two scheduling policies. The first is a single-queue policy, where all requests go into a unified queue, and the dispatcher assigns the head-of-queue request to an available worker. If a request exceeds a predefined time quantum (typically 5–15  $\mu$ s), the system preempts it and returns it to the queue. The

second policy uses multiple queues, where a network subsystem classifies requests by type (e.g., get/scan). It assigns each type its queue and a user-defined 99th percentile latency SLO. The dispatcher selects the queue with the longest waiting time relative to its SLO. Preempted requests return to their respective queues and are placed at the head or tail depending on the distribution of their service times: short-tailed workloads go to the head, while long-tailed or multimodal workloads go to the tail.

In evaluation, researchers compare Shinjuku with IX [7] and ZygOS [55], both of which also use Dune. However, only Shinjuku supports preemption to mitigate HOL blocking. Under synthetic workloads, including fixed-latency (1  $\mu$ s), exponential (mean 1  $\mu$ s), and bimodal (99.5% at 0.5  $\mu$ s, 0.5% at 500  $\mu$ s), Shinjuku consistently delivers the best or near-best performance. In the bimodal case, Shinjuku achieves 5× higher throughput and 50% lower latency, while IX and ZygOS suffer from head-of-line blocking.

Further experiments using RocksDB [60] evaluate get requests (6  $\mu$ s) and scans (240  $\mu$ s for 1000 entries, 1200  $\mu$ s for 5000 entries). In the bimodal workload (99.5% GET, 0.5% SCAN(1000)), Shinjuku again outperforms the others, achieving 6.6× higher throughput and 88% lower latency. In a more balanced bimodal workload (50% GET, 50% SCAN(5000)), Shinjuku demonstrates the importance of combining preemption with multiple-queue scheduling to maintain performance under mixed loads.

## 3.3.2 Perséphone

Perséphone [20] is designed to reduce tail latency in datacenter applications that operate at a microsecond scale and exhibit high service time dispersion (*i.e.*, requests have widely varying processing times). Key-value database applications, for instance, handle multiple request types, each with distinct service time

characteristics. In Redis [57], simple get/put requests typically have a service time of 2  $\mu$ s [53], whereas more complex scan operations can require hundreds of microseconds [36].

Such variation in service times can lead to Head-of-Line (HOL) blocking, where short requests are delayed by long ones, thereby inflating latency. Perséphone uses the slowdown metric to quantify this effect, which is defined as the ratio of the total time a request spends in the system to its service time. For example, if a short request  $(1 \mu s)$  is queued behind a long one  $(500 \mu s)$ , its slowdown is (1+500)/1 = 501, whereas the long request's slowdown is (500 + 1)/500 = 1.002. This asymmetry highlights how long requests can severely delay short ones, but not vice versa.

To address this issue, Perséphone introduces a scheduling policy called DARC (Dynamic Application-aware Reserved Cores), which avoids HOL blocking by dedicating exclusive CPU cores to short requests. The system profiles each request type's service time and uses the average CPU demand under high load conditions to determine how many cores to reserve. It also monitors queue delays and CPU demand variation to adjust these reservations dynamically in response to workload changes.

Requests are classified by type using an external classifier and placed into corresponding queues. The dispatcher selects requests from these queues and assigns them to available application cores. Short requests, with minimal impact on long ones, can execute on any free core, including those reserved. However, long requests are restricted to non-reserved cores to prevent interference with latency-sensitive workloads. This cycle stealing mechanism allows short requests to use reserved resources during bursts temporarily.

Perséphone [20] evaluated workloads with a dispersion of 100× to 1000× between short and long requests under four policies: DARC, d-FCFS, c-FCFS, and PS. DARC consistently delivered lower overall slowdown and latency across all scenarios while reducing peak throughput slightly (by 5%). Under a more stringent SLO,

however, Perséphone achieves higher throughput than the other approaches.

#### 3.3.3 Concord

Concord [33] leverages LLVM passes [39] to automatically instrument applications at compile time by inserting yield points that help mitigate Head-of-Line (HOL) blocking. Concord's design is centered around three key components:

- LLVM Passes: Concord instruments application code using LLVM to insert checks periodically evaluating a preemption flag during request processing. When the flag is set, the application voluntarily yields the current request. This mechanism, known as compiler interrupts, offers a low-overhead alternative to hardware interrupts such as IPIs (Inter-Processor Interrupts).

- **JBSQ**: Concord employs a dispatcher thread to efficiently distribute requests between workers using the JBSQ (Join-Bounded-Shortest-Queue) load-balancing policy. This strategy minimizes contention introduced by the dispatcher and reduces worker idle time by assigning requests to the least loaded queues within bounds.

- **Dispatcher**: Beyond request distribution, the dispatcher can optionally participate in processing requests, though this is primarily beneficial under low-load conditions. More importantly, it is responsible for setting the preemption flags that signal workers to yield, enabling HOL blocking mitigation through cooperative multitasking.

Experimental results demonstrate that Concord achieves higher throughput than Shinjuku due to its lightweight preemption mechanism. However, this comes at the cost of slightly higher tail latency, which is attributable to the characteristics of the JBSQ policy. For instance, under a High workload, where 50% of requests have a 1  $\mu$ s service time and the remaining 50% take 100  $\mu$ s, Concord delivers 20% more

throughput than Shinjuku but incurs a slowdown increase of approximately  $3\times$  for the short requests.

#### 3.3.4 Tiny Quanta

Tiny Quanta builds on a design similar to Concord's, using LLVM passes for instrumentation. However, unlike Concord, Tiny Quanta inserts probes that use the timestamp counter register (e.g., using rdtsc instruction) to track how long each request has been executing locally. If the execution time exceeds a predefined threshold, the worker voluntarily preempts the request. This self-managed approach removes the need for external coordination to trigger preemption.

Tiny Quanta implements a two-level scheduling mechanism. In the first level, a dispatcher assigns requests to worker queues using the Join-Shortest-Queue (JSQ) policy, which reduces contention and improves load balancing. Each worker applies a processor-sharing policy in the second level, enabling fine-grained control over request execution time and reducing head-of-line blocking.

Experimental results show that Tiny Quanta outperforms Shinjuku in both throughput and scalability. Specifically, it achieves  $1.33\times$  and  $2.6\times$  higher throughput than Shinjuku under High and Extreme workloads, respectively. Additionally, thanks to low dispatcher contention and efficient local scheduling, Tiny Quanta scales up to 12 million requests per second (MRPS) using 16 worker cores on workloads with low service time dispersion, significantly outperforming Shinjuku, which scales only up to 2 MRPS under similar conditions.

# Chapter 4

# **Design Space**

This chapter discusses the design space adopted by various systems targeting datacenter application processing and highlights unexplored optimization opportunities. By analyzing the common architectural choices, we seek to identify the trade-offs hindering performance and scalability and set the stage for new design directions.

## 4.1 Motivation

Recent advances in networking have led to transmission rates reaching hundreds of gigabits per second, with terabit links coming soon [11]. Meanwhile, processor speeds have remained relatively stagnant, making it necessary to scale network applications across multiple CPU cores. However, building systems that scale efficiently with core count while maintaining low tail latency remains challenging. Key issues include ensuring balanced load distribution across cores and preventing long-running requests from delaying shorter, latency-sensitive ones.

## 4.2 Request Dispatching and Load Balancing

To address the challenges of scaling datacenter applications on multicore architectures, both industry systems [24, 49] and academic work [3, 7] rely on sharding—partitioning application or protocol state (e.g., TCP control blocks) and assigning each shard to a dedicated core. This strategy, known as share-nothing [55], is typically combined with Receive-Side Scaling (RSS) [61], where the NIC assigns incoming packets to queues based on a hash of the packet's contents (e.g., five-tuple). Each queue maps to a specific core, ensuring that packets from the same flow are processed by the same core. The result is a decentralized scheduling policy known as d-FCFS (Decentralized First-Come, First-Served), where each core independently processes requests from its own queue to completion.

While d-FCFS supports scalable designs, it suffers from two major limitations. First, RSS does not always distribute requests evenly, which leads to load imbalances—some cores become overloaded while others sit idle—resulting in a non-work-conserving system and increased latencies [3]. Second, long requests can block short ones even when there are idle workers, a classic HOL blocking issue [20].

To balance the load across workers, several systems adopt variants of Centralized FCFS (c-FCFS), where all requests are placed in a shared queue and processed by multiple cores in arrival order [20, 36]. While this approach improves load distribution, it introduces its own challenges: bursts of long requests can monopolize all cores, delaying short ones and still causing HOL blocking. Systems like Shinjuku [36] and Perséphone [20] approximate c-FCFS by using a dedicated dispatching core that distributes requests to workers via a JIQ (Join Idle Queue) policy. Tardis [69], though operating with multiple NIC queues, also approximates c-FCFS by relying on a globally shared queue accessible to all workers.

Although c-FCFS provides theoretically optimal tail latency [67], it suffers from a scalability bottleneck, as the dispatcher or shared queue becomes a point of

Figure 4.1: Simulation of different overheads in nanoseconds to centralized dispatching. The results show 99.9th latency on a function of load using 1 dispatcher, 14 workers and requests with service time of 1  $\mu$ s.

contention [25, 46].

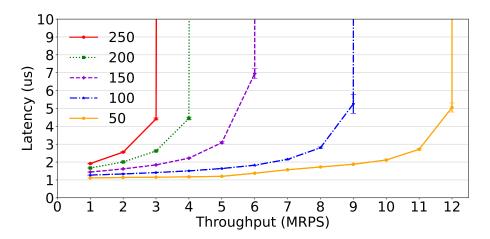

We extend the simulator provided by [46] to evaluate the scalability limitations of the c-FCFS policy by modeling a system with one dispatcher and 14 workers. This configuration reflects real-world deployments that employ c-FCFS [20, 36]. To simulate dispatching overheads, the dispatcher waits for x nanoseconds after receiving a new request before forwarding it. Figure 4.1 shows the 99.9th percentile tail latency as a throughput function, using requests with a service time of 1  $\mu$ s. The results demonstrate that even a few nanoseconds of dispatching overhead can significantly impact system throughput and request tail latency.

To reduce this contention, Concord and Tiny Quanta adopt JBSQ (Join-Bounded-Shortest-Queue) and JSQ (Join-Shortest-Queue) policies, which reduce dispatcher contention at the cost of increased tail latency. Tardis takes a different approach: each worker dequeues N requests at a time from the global queue into a local queue. Smaller values of N improve load balance but increase contention; larger values reduce contention but worsen balance, making N a tunable parameter that controls how closely Tardis approximates c-FCFS.

Synergy takes a different approach. It adopts a decentralized dispatching

strategy where each worker receives requests directly from its NIC queue, thus avoiding the scalability issues of c-FCFS. To compensate for the inherent imbalance of multiple queues, Synergy employs two complementary techniques: work stealing [46,55] and a global wait queue for preempted long requests. In workloads with high service time dispersion, equalizing queue lengths with work stealing is insufficient. For example, a worker handling a single long request may use more CPU cycles to process it than one handling many short requests. The global wait queue enables long requests to be redistributed among workers, improving balance beyond what static queue assignment with work stealing allows.

## 4.3 HOL-Blocking Mitigation

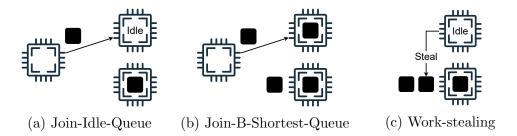

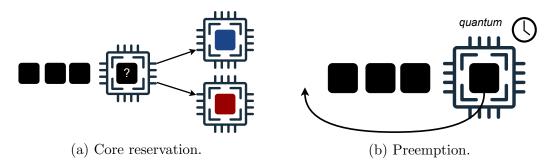

Figure 4.2: HOL Blocking mitigation strategies.

As shown in Figure 4.2, existing systems that address HOL blocking generally fall into two main categories: core-reservation and preemptive approaches.

Perséphone [20] is a recent system that dedicates cores exclusively to processing short requests. These reserved cores remain idle when there are no short requests to process. While this approach reduces overhead for the workers and prevents long requests from delaying short ones, it shifts complexity to the dispatcher, which must classify incoming requests and place them in separate queues, turning it into a potential bottleneck of the system.

Preemptive approaches, such as Shinjuku, Concord, Tardis, and Tiny Quanta,

enforce a fixed-time quantum for each request, limiting how long any request can run uninterrupted. This processor-sharing model is theoretically better for workloads with high dispersion [67]. However, enforcing it adds overhead. Shinjuku and Concord rely on dispatchers to interrupt workers—Shinjuku uses virtualization features to reduce IPI (Inter-Processor Interrupt) overhead. Concord, on the other hand, introduces Compiler Interrupts (CI), enabling workers to yield voluntarily based on a shared flag. Tiny Quanta uses CI alone, removing the dispatcher's role in interrupting. Tardis employs hardware timers and recent CPU features like user-level interrupts [64] to preempt workers periodically.

SYNERGY also uses preemption but improves upon prior designs by using job-aware conditional preemption. It interrupts long requests only when other jobs are waiting in the worker's queue, which avoids unnecessary context switches and reduces the system overhead.

## 4.4 Application Awareness

Most existing approaches are application-agnostic and treat all requests uniformly, ignoring valuable information that the application can provide [35, 55, 69]. This lack of awareness forfeits opportunities to make more informed scheduling and resource allocation decisions. By incorporating application-level information—such as request type, expected processing time, or priority—systems can adapt more effectively to workload characteristics, leading to more efficient resource usage and improved performance.

Some of the recent systems like Perséphone [20] and Shinjuku [36] distinguish request types. Perséphone classifies requests at dispatch time and assigns each worker to a specific class, allowing workers to process requests without interruption. However, classification is done externally by the dispatcher, duplicating effort the application later repeats. Shinjuku supports multiple queues per worker but relies

on the network subsystem—also running on the dispatcher—for classification.

Unlike prior work, SYNERGY uses direct application feedback to classify requests, eliminating the need for centralized classification. This approach eliminates redundancy and enables lightweight cooperation between the application and the scheduler. It also broadens the range of request types that can be treated differently, including those whose service times depend on internal state or application-specific factors (e.g., search term popularity [18]).

## 4.5 Extra Core and Optimizations

Many designs rely on a dedicated core for auxiliary tasks such as dispatching, request classification, or triggering preemptions. However, since this core handles every request, it often becomes a scalability bottleneck. In Perséphone, for example, the dispatching core is also responsible for periodically adjusting resource allocation (e.g., resizing the set of reserved cores for short requests), which temporarily pauses dispatching and increases queueing delays [20].

SYNERGY, like some prior systems, reserves an extra core for background tasks. Importantly, this core remains off the request-processing path, ensuring it does not limit scalability. It performs two key functions: (i) interrupting workers processing long requests when needed and (ii) monitoring the wait queue to ensure long requests make progress. These functionalities provide the following benefits:

Reduced Interrupt Frequency: Synergy minimizes preemptions by interrupting a long request only when there is a new request waiting on the worker's queue. This approach contrasts with prior systems that interrupt any request exceeding a fixed quantum, imposing constant overhead even when unnecessary. Fewer interrupts not only reduce the latency for long requests but also improve system throughput. Furthermore, Synergy ensures that short requests execute to completion without requiring a large quantum. This not only avoids the impact of

Table 4.1: Comparison of Synergy and prior systems across key scheduling design dimensions.

|                         | Synergy                            | Shinjuku [36]                               | Perséphone [20]                                                            | Concord [33]                                | Tardis [69]                       | Tiny Quanta [45]     |

|-------------------------|------------------------------------|---------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|-----------------------------------|----------------------|

| Request Dispatching     | Hardware/Decentralized             | Software/Centralized                        | Software/Centralized                                                       | Software/Centralized                        | Hardware/Decentralized            | Software/Centralized |

| Load Balancing          | Work Stealing and<br>Wait Queue    | ЛQ                                          | Reserved JIQ                                                               | JBSQ                                        | Global Queue and<br>Work Stealing | JSQ                  |

| HOL Blocking Mitigation | Preemptive                         | Preemptive                                  | Core reservation                                                           | Preemptive                                  | Preemptive                        | Preemptive           |

| Application Aware       | Yes                                | Yes                                         | Yes                                                                        | No                                          | No                                | No                   |

| Extra-Core Function     | Worker Interrupt and<br>Monitoring | Request Dispatching<br>and Worker Interrupt | Request Classification and<br>Dispatching, and Core<br>Reservation Updates | Request Dispatching<br>and Worker Interrupt | -                                 | Request Dispatching  |

| Interrupt Frequency     | Job-aware                          | Timed                                       | -                                                                          | Timed                                       | Timed                             | Timed                |

| Quantum Size            | Dynamic                            | Static                                      | -                                                                          | Static                                      | Static                            | Static               |

premature interruptions on short requests but also enables the use of small quantum.

Dynamic Quantum Sizing: Thanks to the application feedback, SYNERGY dynamically adjusts the quantum size based on workload conditions. By identifying the type of request each worker is processing and measuring the service time of short requests, SYNERGY can adjust the quantum size in real time. This adaptive strategy avoids the limitations of a fixed quantum: if the quantum is too large, short requests experience unnecessary delays when the worker is processing a long request; if too small, the system incurs excessive preemptions and added overhead. Also, operators can fine-tune quantum sizing parameters to prioritize specific request types according to application needs.

Together, the design choices in Synergy allow it to combine the scalability of decentralized dispatching with the latency benefits of intelligent, application-aware preemption, effectively mitigating HOL blocking without sacrificing performance. Table 4.1 summarizes the design space and compares Synergy with the existing systems.

# Chapter 5

## **SYNERGY**

This chapter introduces Synergy, a cooperative, application-aware scheduling system that uses direct feedback from applications to prioritize short requests, dynamically adjusts scheduling parameters, and avoids unnecessary preemptions. Synergy delivers fast, low-overhead, and scalable scheduling optimized explicitly for datacenter applications with microsecond-scale workloads, as we outline in Chapter 4. By combining efficient scheduling mechanisms with lightweight coordination, Synergy addresses the performance demands of modern low-latency and high-throughput environments.

## 5.1 Design

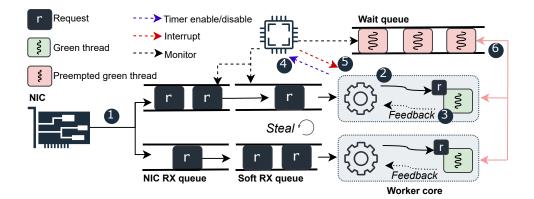

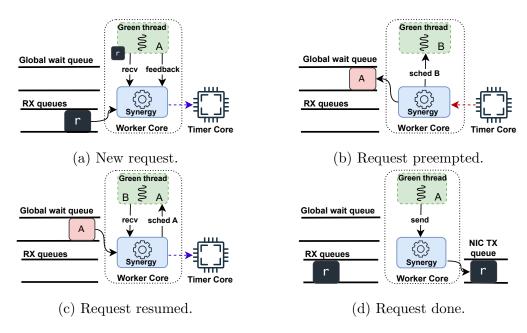

Figure 5.1 presents an overview of Synergy and illustrates the interaction between its main components. Synergy receives incoming requests through multiple NIC queues (e.g., using RSS [61], Flow Director [52], or programmable NICs [37]). Each NIC queue is assigned to a single worker to prevent concurrent access to the hardware queues. Synergy also maintains a global wait queue to store preempted requests. For clarity, we describe the system using only two request types—short and long—but it can be extended to more types by using multiple wait queues with

Figure 5.1: SYNERGY overview. Solid lines represent request path and dashed lines indicate timer core queue monitoring and interactions between timer core and worker cores.

priority levels based on request type.

To enable efficient work stealing, each worker transfers batches of requests from its NIC queue to a local software queue. It then processes each request using a reusable *green thread*, unlike prior systems that allocate a new green thread per request [33, 36, 69]. Short requests always run to completion and are never preempted. In contrast, when a long request is interrupted, Synergy moves its associated green thread to the wait queue and switches to a new green thread to process new requests.

Any worker can access the wait queue to resume preempted requests to improve load distribution across cores. Workers also compute the average service time of short requests so that SYNERGY can dynamically calculate the quantum for long requests. The goal is to set the quantum so that a short request queued behind a long one is not delayed for more than the typical service time of a short request. Operators can adjust this behavior using a configurable multiplier to increase the CPU time allocated to long requests and reduce their total time in the system. Section 6.3.2 evaluates the impact of this multiplier.