# Approximate Computing: Contributions to the Design of Arithmetic Circuits and Instruction-Set Architectures

# Daniela Luiza Catelan

Advisor: Dr. Ricardo Ribeiro dos Santos

Federal University of Mato Grosso do Sul - UFMS College of Computing - FACOM January 15, 2025

# Approximate Computing: Contributions to the Design of Arithmetic Circuits and Instruction-Set Architectures

# Daniela Luiza Catelan

Advisor: Dr. Ricardo Ribeiro dos Santos

A thesis presented to the Ph.D. Program in Computer Science at the College of Computing of the Federal University of Mato Grosso do Sul, as a partial requirement for attaining the Doctorate degree.

#### Thesis Committee:

Prof. Dr. Ricardo Ribeiro dos Santos - FACOM/UFMS - Advisor

Prof. Dra. Liana Dessandre Duenha Garanhani - FACOM/UFMS - Internal Member

Prof. Dr. Lucas Francisco Wanner - IC/UNICAMP - External Member

Prof. Dr. Ricardo dos Santos Ferreira - DPI/UFV - External Member

Prof. Dr. Edson Antonio Batista - FAENG/UFMS - External Member

Prof. Dra. Nahri Balesdent Moreano - FACOM/UFMS - Substitute Member

Federal University of Mato Grosso do Sul - UFMS College of Computing - FACOM January 15, 2025

### Abstract

The growing demand for computing power, coupled with the limitations of the end of the Dennard scale, has challenged designers to find alternative solutions to maintain performance within energy and cost limits. Approximate computing (AC) has emerged as a promising approach to balance performance and energy efficiency in error-tolerant applications. However, many AC techniques focus on specific problems or require much intervention from the programmer. This work identified gaps that were transformed into research opportunities. One is related to approximate arithmetic circuits, which focus on single-bit operations, limiting the analysis of these circuits' physical behavior, accuracy, and performance on real platforms with larger inputs and outputs. There are also limitations in the loop perforation technique since once the perforation degree (pd) is established, the application metrics will improve only at the cost of accuracy. Adopting a strategy in which pd can use approximate hardware resources would overcome this limitation, and greater flexibility would be obtained without forcing additional compilation steps. There is little exploration of the use of approximate instructions, especially in the context of floating point operations, leaving an implementation gap that can be solved by introducing an additional level of approximation, replacing precise (non-approximate) instructions with approximate instructions, thus offering a hardware-level approximate technique over a source code that is already (or not) approximated by a software-level technique. Thus, this work aims at design space exploration (DSE) at different levels of abstraction, investigating the impact of AC on approximate arithmetic circuits, approximate instructions, loop perforation techniques, and approximate mathematical functions. In addition, extensions of the RISC-V architecture instruction set with support for AC are designed. AC techniques were integrated into a widely used platforms, such as SPIKE and ACCEPT, to provide a flexible and efficient infrastructure for developing of approximate systems. The results demonstrate that AC can significantly improve performance and energy efficiency without substantially compromising the accuracy of the systems. This work contributes to new approximate instructions, arithmetic circuits, and an energy model for approximate instructions. It explores the feasibility of these techniques in mathematical functions and control structures (loop) in applications that demand high performance but tolerate controlled errors.

**Keywords:** approximate computing, approximate arithmetic circuits, approximate instructions, loop perforation, approximate mathematical functions

### Resumo

O crescimento da demanda por poder computacional, aliado às limitações do fim da escala de Dennard, desafiou os projetistas a encontrar soluções alternativas para manter o desempenho dentro dos limites de energia e custo. A computação aproximada (CA) emerge como uma abordagem promissora para equilibrar desempenho e eficiência energética em aplicações que toleram erros. No entanto, muitas técnicas de CA focam em problemas específicos ou exigem muita intervenção do programador. Este trabalho identificou lacunas que foram transformadas em oportunidades de pesquisa. Uma delas está relacionada aos circuitos aritméticos aproximados, que focam em operações de um único bit, limitando a análise do comportamento fisico, da precisão e do desempenho desses circuitos em plataformas reais com entradas e saídas maiores. Há também limitações na técnica de perfuração de loops, visto que uma vez que o grau de perfuração (pd) é estabelecido, as métricas do aplicativo melhorarão apenas ao custo da precisão. Ao adotar uma estratégia em que o pd possa usar recursos de hardware aproximado, esta limitação seria mitigada, além de obter uma maior flexibilidade sem forçar nenhuma etapa de compilação adicional. Há pouca exploração sobre o uso de instruções aproximadas, especialmente no contexto de operações de ponto flutuante, deixando uma lacuna de implementação, que poder ser resolvida com a introdução de um nível adicional de aproximação, substituindo instruções precisas (não aproximadas) por instruções aproximadas, oferecendo desta forma, uma técnica aproximada de nível de hardware sobre um código-fonte que já é (ou não) aproximado por uma técnica de nível de software. Desta forma, este trabalho tem por objetivo a exploração do espaço de projeto (DSE) em diferentes níveis de abstração, investigando o impacto da CA em circuitos aritméticos aproximados, instruções aproximadas e técnicas de perfuração de loops e de funções matemáticas aproximadas. Além disso, são projetadas extensões do conjunto de instruções da arquitetura RISC-V com suporte à CA. A integração de técnicas de CA foi realizada em plataformas amplamente utilizadas, como SPIKE e ACCEPT, para proporcionar uma infraestrutura flexível e eficiente no desenvolvimento de sistemas aproximados. Os resultados demonstram que a CA pode melhorar significativamente o desempenho e a eficiência energética, sem comprometer substancialmente a precisão dos sistemas. Este trabalho contribui com novas instruções aproximadas, circuitos aritméticos e um modelo energético para instruções aproximadas, além de explorar a viabilidade dessas técnicas em funções matemáticas e estruturas de controle (loop) em aplicações que exigem alto desempenho, mas que toleram erros controlados.

Palavras-Chave: computação aproximada, circuitos aritméticos aproximados, instruções aproximadas, loop perforation, funções matemáticas aproximadas

# Acknowledgements

I could not begin my thanks without first thanking God. There were countless challenges during my doctorate, but God was always with me, blessing me and covering me with wisdom to overcome each obstacle that appeared.

I thank my children, José Luiz and Maria Luiza, for understanding my moments of absence, lousy mood, and impatience. But I am even more grateful for their encouragement, support, and strength.

I am immensely grateful to my parents, Luiz and Neuza, who were my support network. They found a way to be there even when busy with their tasks, making the path easier.

From the bottom of my heart, I thank Professor Ricardo for his excellent guidance, the weekly meetings that kept me focused, and his patience and dedication to understanding the delays in completing the scheduled activities and for never giving up on guiding me.

I must thank my lab colleagues, such as Samuel, who played a valuable role in part of my project, and Guilherme Gloriano, for the chats to relax and share the worries of doctoral students and for the countless help with Overleaf.

I would also like to thank Professor Liana for her participation and support throughout the entire process of my doctorate.

Finally, so as not to run the risk of forgetting anyone and before the tears flow, I would like to thank all those who, directly or indirectly, were with me on this journey.

# Contents

| Li | st of       | Figures                                             | 9  |

|----|-------------|-----------------------------------------------------|----|

| Li | ${f st}$ of | Tables                                              | 13 |

| Li | ${f st}$ of | Acronyms                                            | 14 |

| 1  | Inti        | roduction                                           | 19 |

| 2  | App         | proximate Computing                                 | 22 |

|    | 2.1         | Contextualization                                   | 22 |

|    | 2.2         | Organization of AC Techniques                       | 23 |

|    | 2.3         | Software Support for Approximate Computing          | 26 |

|    | 2.4         | Hardware Support for Approximate Computing          | 28 |

|    | 2.5         | Software/Hardware Support for Approximate Computing | 30 |

|    | 2.6         | Architectural Support for Approximate Computing     | 33 |

|    | 2.7         | Final Remarks                                       | 33 |

| 3  | Des         | ign of Approximate Arithmetic Circuits              | 35 |

|    | 3.1         | Contextualization                                   | 35 |

|    | 3.2         | Approximate Arithmetic Circuit Designs              | 36 |

|    | 3.3         | Experimental Setup, Results, and Discussion         | 38 |

|    |             | 3.3.1 Accuracy Results                              | 42 |

|   |     | 3.3.2  | Area Usage                                     | 45        |

|---|-----|--------|------------------------------------------------|-----------|

|   |     | 3.3.3  | Power Dissipation                              | 47        |

|   | 3.4 | Final  | Remarks                                        | 50        |

| 4 | App | proxim | ate Instructions                               | <b>52</b> |

|   | 4.1 | Conte  | xtualization                                   | 52        |

|   | 4.2 | RISC-  | V Instruction Set                              | 53        |

|   | 4.3 | Appro  | eximate Instructions Design                    | 54        |

|   |     | 4.3.1  | Approximate Integer Instructions               | 54        |

|   |     | 4.3.2  | Approximate Floating Point Instruction         | 58        |

|   | 4.4 | Tools  | Extension                                      | 60        |

|   |     | 4.4.1  | SPIKE ISA SIM                                  | 60        |

|   |     | 4.4.2  | Prof5                                          | 66        |

|   |     | 4.4.3  | ACCEPT                                         | 69        |

|   | 4.5 | Final  | Remarks                                        | 71        |

| 5 | App | oroxim | nate Computing Software-Hardware Approach      | 72        |

|   | 5.1 | Conte  | xtualization                                   | 72        |

|   | 5.2 | Instru | ction-Level Loop Perforation - ILLP            | 74        |

|   |     | 5.2.1  | Loop Perforation Approximation Technique       | 74        |

|   |     | 5.2.2  | Instruction-Level Loop Perforation Design      | 75        |

|   |     | 5.2.3  | Experimental Setup                             | 77        |

|   |     | 5.2.4  | Results and Discussion                         | 79        |

|   | 5.3 | Instru | ction-Level Approximate Function - ILAF        | 86        |

|   |     | 5.3.1  | Instruction-Level Approximate Functions Design | 87        |

|   |     |        | 5.3.1.1 Approximate Functions Design           | 88        |

|   |     | 5.3.2  | Experimental Setup                             | 89        |

|   |     | 5.3.3 Results and Discussion | 90 |

|---|-----|------------------------------|----|

|   | 5.4 | Final Remarks                | 95 |

| 6 | Cor | nclusions                    | 96 |

|   | 6.1 | Specific Conclusions         | 96 |

|   | 6.2 | Limitations of the Study     | 97 |

|   | 6.3 | Thesis Contributions         | 98 |

|   | 6.4 | Future Work                  | 99 |

# List of Figures

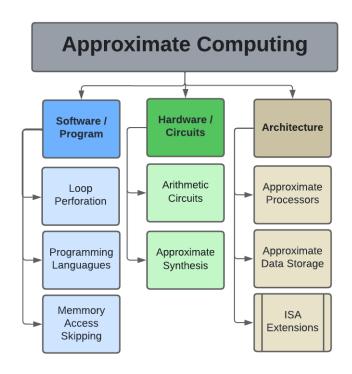

| 1.1 | Examples of approximate computing techniques: software, hardware, architecture, and software/hardware. Source: author | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Overall structural diagram of the thesis chapters. Source: author                                                     | 21 |

| 2.1 | Classification of AC proposed by Palem and Lingamneni. Source: [49]                                                   | 24 |

| 2.2 | Classification of AC techniques proposed by Shafique et al. Source: [63]                                              | 24 |

| 2.3 | Classification of AC techniques proposed by Vasileios et al. and Xu et al. Source: [32, 79]                           | 25 |

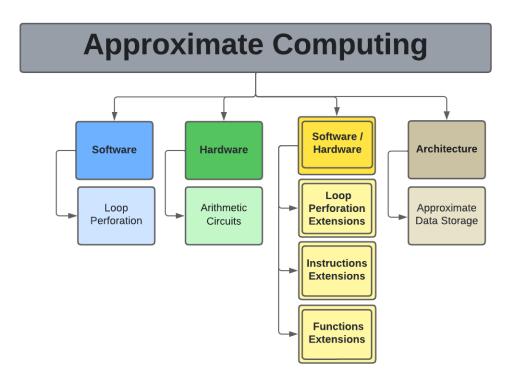

| 2.4 | Proposed taxonomy for approximate computing. Source: author                                                           | 26 |

| 2.5 | EnerJ hardware model. Source: [59]                                                                                    | 31 |

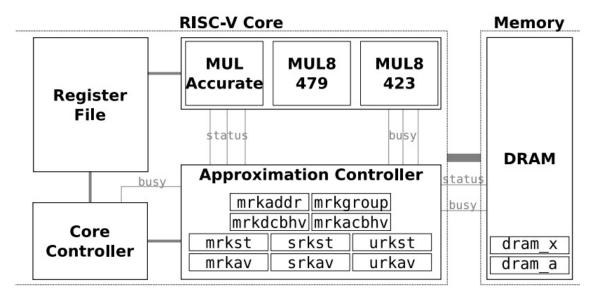

| 2.6 | RISK-5 hardware schematic. Source: [21]                                                                               | 31 |

| 2.7 | QUORA microarchitecture. Source: [73]                                                                                 | 32 |

| 3.1 | 1-bit accuracy adder in VHDL code. Source: author                                                                     | 40 |

| 3.2 | 1-bit approximate adder InXA3 in VHDL code. Source: author                                                            | 40 |

| 3.3 | 2-bit mixed circuit in VHDL code. Source: author                                                                      | 41 |

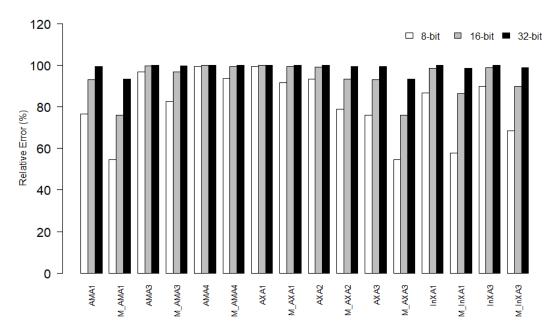

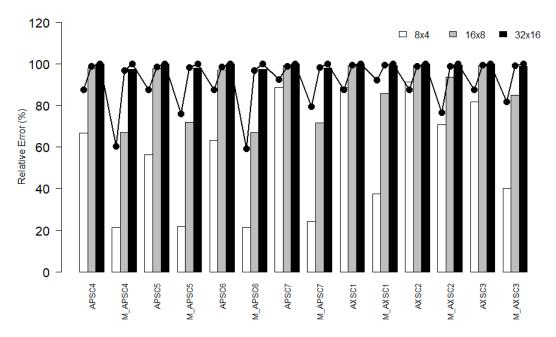

| 3.4 | Accuracy result (relative error percentage) for adder circuits. Source: author                                        | 42 |

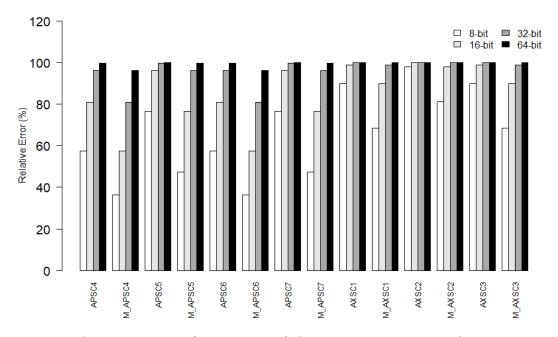

| 3.5 | Accuracy result (relative error) for subtractor circuits. Source: author                                              | 43 |

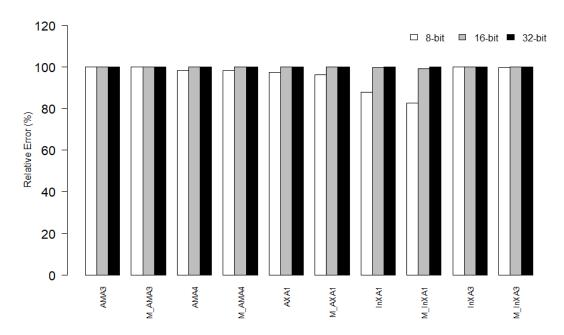

| 3.6 | Accuracy result (relative error percentage) for multiplier circuits. Source: author                                   | 44 |

| 3.7 | Accuracy results (relative error percentage) for divider circuits. Source: author                                     | 44 |

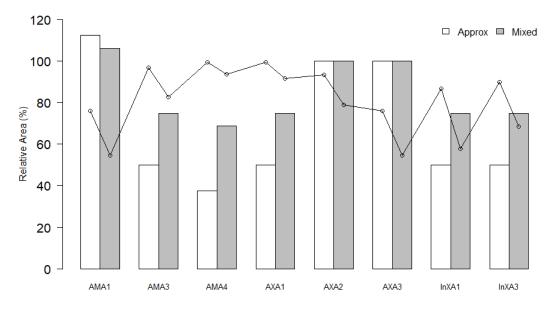

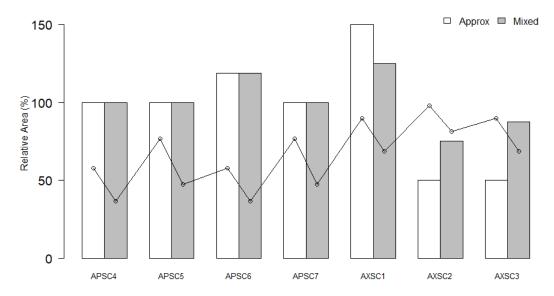

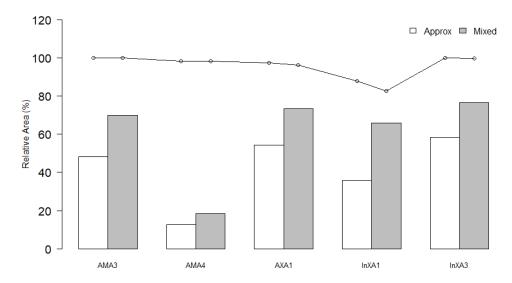

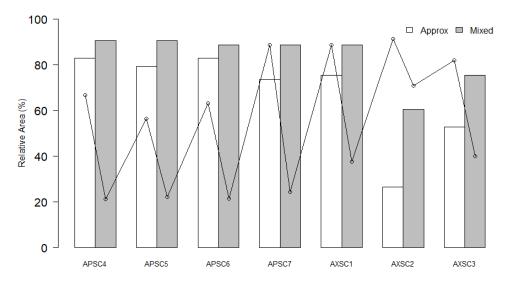

| 3.8  | Percentage of relative area of approximate circuits for 8-bit adders with relative error. Source: author       | 45 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Percentage of relative area of approximate circuits for 8-bit subtractor with relative error. Source: author   | 46 |

| 3.10 | Percentage of relative area of approximate circuits for 8-bit multiplier with relative error. Source: author   | 47 |

| 3.11 | Percentage of relative area of approximate circuits for 8-bit divider with relative error. Source: author      | 47 |

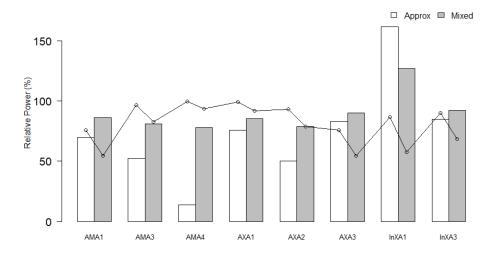

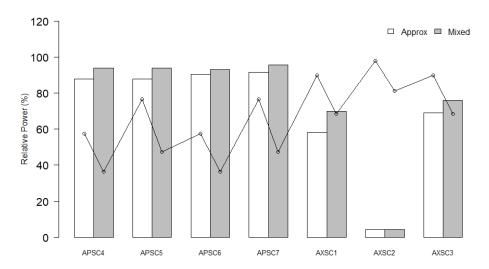

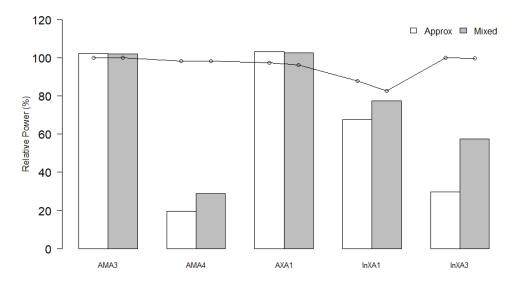

| 3.12 | Percentage of relative power of approximate circuits for 8-bit adder with relative error. Source: author       | 48 |

| 3.13 | Percentage of relative power of approximate circuits for 8-bit subtractor with relative error. Source: author  | 48 |

| 3.14 | Percentage of relative power of approximate circuits for 8-bit multiplier with relative error. Source: author  | 49 |

| 3.15 | Percentage of relative power of approximate circuits for 8-bit divider with relative error. Source: author     | 50 |

| 4.1  | Workflow for approximate instructions design and evaluation. Source: author                                    | 53 |

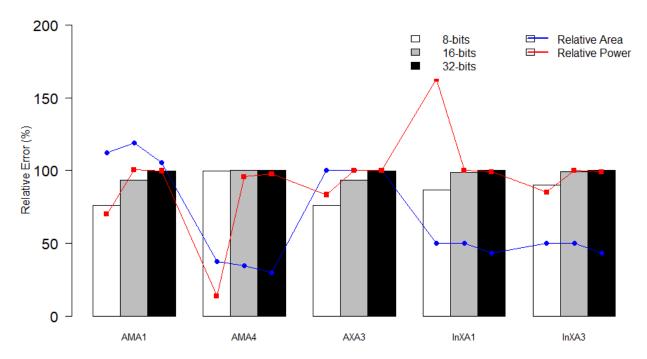

| 4.2  | Percentages of relative area, relative power, and relative error in approximate adder circuits. Source: author | 55 |

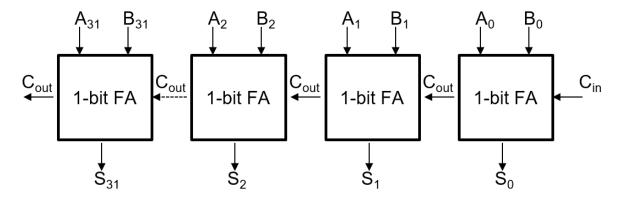

| 4.3  | 32-bits full adder (FA). Source: Based on [52]                                                                 | 56 |

| 4.4  | 4-bits multiplication. Source: author                                                                          | 56 |

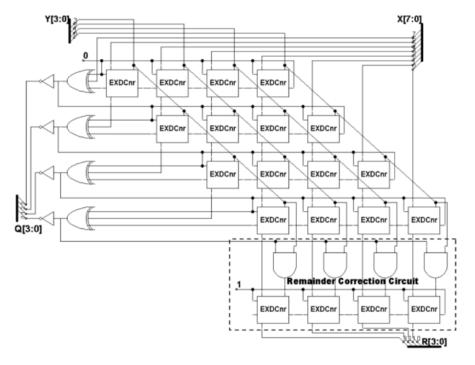

| 4.5  | 8x4-bits divider. Source: [13]                                                                                 | 57 |

| 4.6  | Exact subtractor block for division. Source: [13]                                                              | 57 |

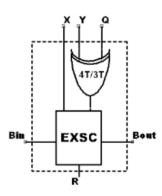

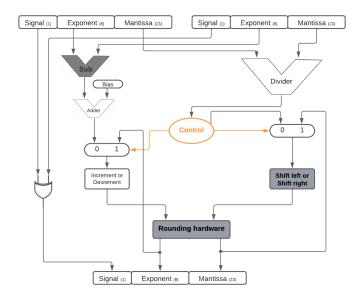

| 4.7  | Block diagram: FP addition and subtraction hardware. Source: Based on [52]                                     | 59 |

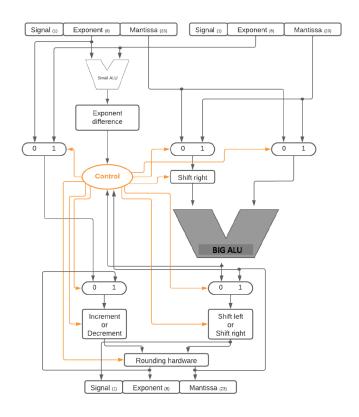

| 4.8  | Block diagram: FP multiplier hardware. Source: Based on [52]                                                   | 59 |

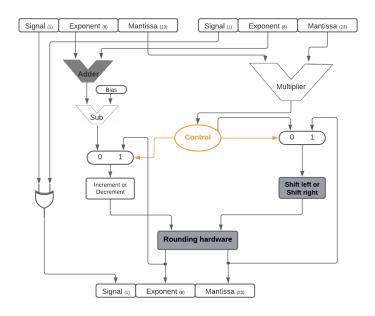

| 4.9  | Block diagram: FP divider hardware. Source: Based on [52]                                                      | 60 |

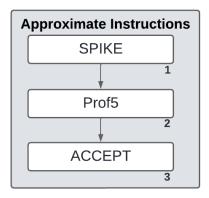

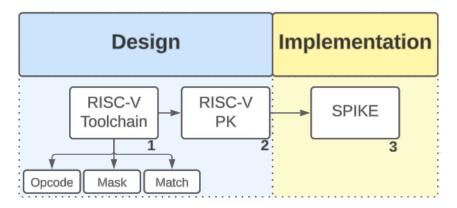

| 4.10 | Flowchart for the design and implementation of approximate instructions. Source: author                        | 61 |

| 4.11 | Mask and match approximate instructions. Source: author                                                        | 62 |

| 4.12 | Functionality of the approximate <b>addx</b> instruction. Source: author                                          | 62 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 4.13 | Functionality of the approximate $\mathbf{subx}$ instruction. Source: author                                      | 63 |

| 4.14 | Functionality of the approximate $\mathbf{mulx}$ instruction. Source: author                                      | 64 |

| 4.15 | Functionality of the approximate $\mathbf{divx}$ instruction. Source: author                                      | 66 |

| 4.16 | Functionality of the approximate $\mathbf{rem}\mathbf{x}$ instruction. Source: author                             | 67 |

| 4.17 | Approximate addition operations used in the BIG ALU of the approximate FP addition hardware. Source: author       | 68 |

| 4.18 | Approximate subtraction operations used in the BIG ALU of the approximate FP subtraction hardware. Source: author | 68 |

| 4.19 | Approximate multiply operations of the approximate FP multiplier hardware. Source: author                         | 69 |

| 4.20 | Approximate division operations of the approximate FP divider hardware. Source: author                            | 69 |

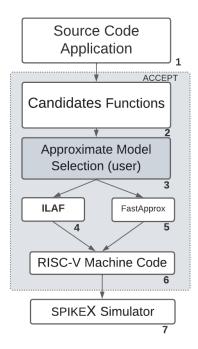

| 4.21 | ACCEPT. Source: author                                                                                            | 71 |

| 5.1  | Original loop and after applying loop perforation. Source: author                                                 | 74 |

| 5.2  | LP with ADDX function call and ADDX function. Source: author                                                      | 75 |

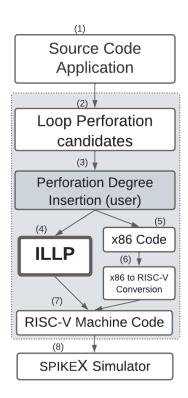

| 5.3  | Workflow and toolset to apply the ILLP technique. Source: author. $\ .$                                           | 76 |

| 5.4  | RISC-V assembly code result of the LP. Source: author                                                             | 77 |

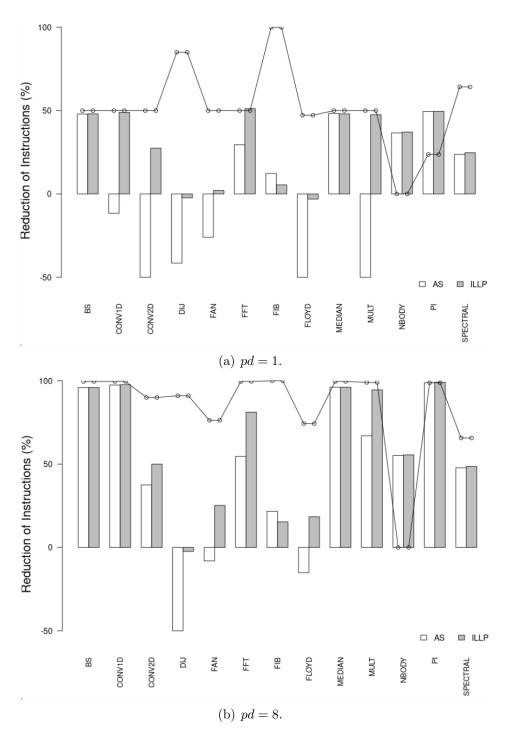

| 5.5  | AS and ILLP instructions percentage reduction for each application. Source: author                                | 81 |

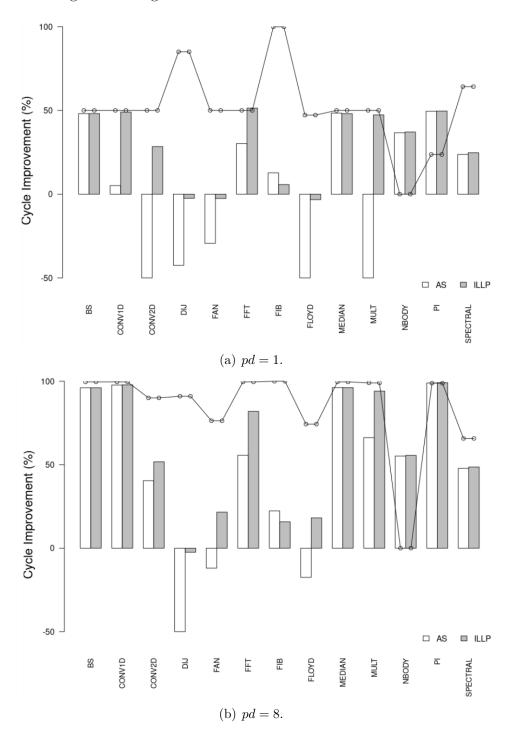

| 5.6  | AS and ILLP cycle improvement percentage for each application. Source: author                                     | 82 |

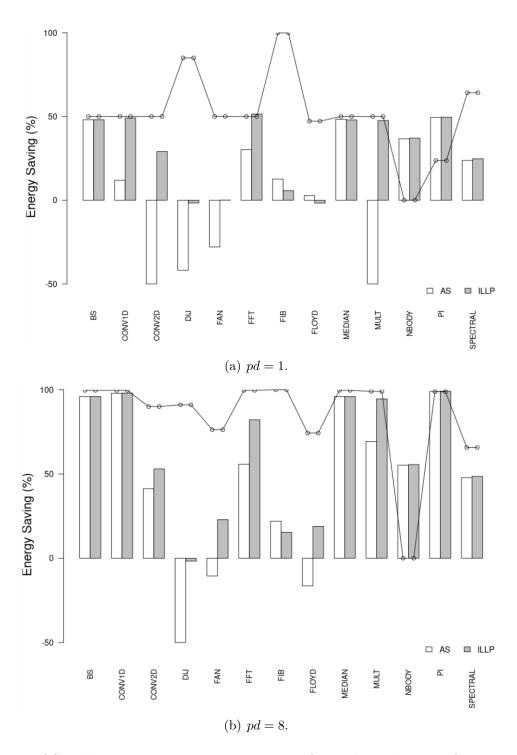

| 5.7  | AS and ILLP energy saving percentage for each application. Source: author.                                        | 84 |

| 5.8  | Percentage reduction for instructions, cycles, and energy by technique. Source: author                            | 85 |

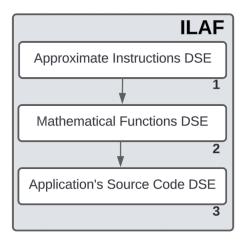

| 5.9  | ILAF design workflow. Source: author                                                                              | 87 |

| 5.10 | Code snippet of the FastLog $_2$ function. Source: author                                                         | 88 |

| 5 11 | ACCEPT approximate functions workflow. Source: author                                                             | 91 |

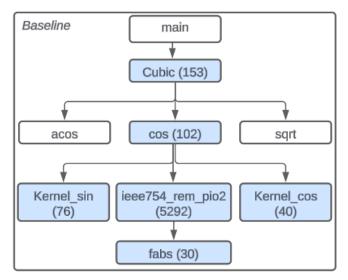

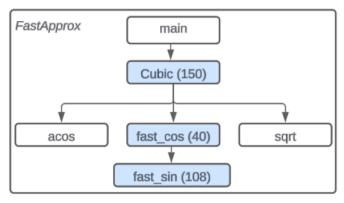

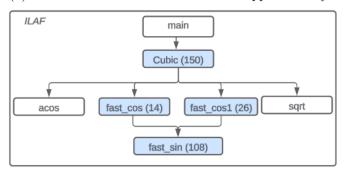

| 5 | .12 | Call | flow        | of the    | cosine   | functi | on of | f C | UBI | Сι | using | gВ | asel | ine | , F | ast. | Ap | pro | x, |    |   |

|---|-----|------|-------------|-----------|----------|--------|-------|-----|-----|----|-------|----|------|-----|-----|------|----|-----|----|----|---|

|   |     | and  | <b>ILAF</b> | '. Source | ce: autl | nor    |       |     |     |    |       |    |      |     |     |      |    |     |    | 9; | 3 |

# List of Tables

| 2.1 | Applications, platforms, domains, and metrics of AxBench. Source: [81]                                       | 28 |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison among AXA, AMA, and InXA adders. Source: [80, 67]                                                 | 29 |

| 2.3 | Comparison between AXSC and APSC subtractor. Source: [24]                                                    | 29 |

| 3.1 | Logical expressions for approximate adders. Source: author                                                   | 37 |

| 3.2 | Logical expressions for the approximate subtractors. Source: author                                          | 37 |

| 3.3 | Approximate $2 \times 2$ multiplier truth table. Source: [31]                                                | 38 |

| 4.1 | RISC-V instruction formats. Source: [52]                                                                     | 54 |

| 4.2 | Layout of some RISC-V arithmetic instructions. Source: [52]                                                  | 54 |

| 4.3 | Logical expressions of the subtractor block used in division. Source: author.                                | 58 |

| 4.4 | Approximate instruction opcodes. Source: author                                                              | 61 |

| 4.5 | Cycles and power results of non-approximate and approximate instructions. Source: author                     | 70 |

| 5.1 | Applications summary. Input apps, Output apps, LP in Hotspots, Has nested loops, Position LP. Source: author | 78 |

| 5.2 | Output, number of instructions, number of cycles, and energy. Source: author                                 | 79 |

| 5.3 | Relative Error. Source: author                                                                               | 80 |

| 5.4 | Selected approximate instructions and MAPE of each mathematical function. Source: author                     | 89 |

| 5.5 | Summary of mathematical functions in each application. Source: author.                                       | 90 |

| 5.6 | Percentage improvements of the applications running the ILAF approach compared to the BL. Source: author                         | 91 |

|-----|----------------------------------------------------------------------------------------------------------------------------------|----|

| 5.7 | Coverage and power improvement of ILAF compared to FAl. Source: author                                                           | 92 |

| 5.8 | Excerpt from the code of the "transit_surface" function (FBENCH application) using the <i>FastApprox</i> library. Source: author | 94 |

| 5.9 | Excerpt from the code of the "transit_surface" function (FBENCH application) using $ILAF$ . Source: author                       | 94 |

# List of Acronyms

**AC** - Approximate Computing

ALE - Total Logic Elements Approximate

**AMA** - Approximate Mirror Adder

ANN - Artificial Neural Networks

**AO** - Approximate Output

**AP** - Power Approximate Circuits

**APDr** - Approximate Divider

**APE** - Approximate Processing Elements

**APSC** - Approximate Subtractor

**AS** - ACCEPT-SPIKE

**ASIC** - Application Specific Integrated Circuits

**AXA** - Approximate XOR/XNOR - based Adder

AXSC - Approximate Subtractor Cell

$\mathbf{BL}$  - Baseline

BO - Output Baseline

**CAPE** - Completely Accurate Processing Element

**CF** - Correction Factor

CPU - Central Process Unit

**DCT** - Discrete Cosine Transform

**DP** - Dynamic Power

**DRAM** - Dynamic Random Access Memory

**DSE** - Design Space Exploration

**ED** - Error Distance

**EDP** - Energy Delay Product

**ELE** - Total Logic Elements Accurate

**EO** - Accurate Circuit Outputs

**EP** - Power Accurate Circuits

ER - Error Rate

**ESA** - Equal Segmentation Adder

FA - Full Adder

FAl - FastApprox library

FP - Floating Point

FPGA - Field Programmable Gate Array

**GPU** - Graphics Processing Unit

**HW/SW** - Hardware-Software Interface

I - Innermost

$\mathbf{I}_{\mathbf{Approx}}$  - Floating Point Approximate Instructions

IC - Inexact Computation

**ILAF** - Instruction-Level Approximate Functions

ILLP - Instruction-Level Loop Perforation

InXA - Inexact Adder Cells

**IOP** - I/O Power

$\mathbf{I_R}$  - Replaced Instructions

**ISA** - Instruction Set Architecture

**LI** - Loop Interpolation

LOA - Lower Part or Adder

**LP** - Loop Perforation

LSB - Least Significant Bit

MAPE - Mixed Accuracy Processing Elements

MLC - Multi-Level Cell Model

**MRED** - Mean Relative Error Distance

**NED** - Normalized Error Distance

NN - Nearest Neighbor

O - Outermost

**PD** - Power Dissipation

$\mathbf{P_{instr}}$  - Percentage Instruction Group

$\mathbf{Power_{ap}}$  - Power Instruction Approximate

$\mathbf{Power_{Diff}}$  - Difference in Percentage

$\mathbf{Power_{imp}}$  - Power Improvement

$\mathbf{Power_{nap}}$  - Non-approximated Instructions

**Q** - Quotient

QUORA - Quality Programmable Vector Processors for Approximate Computing

$\mathbf{R}$  - Remainder

**RA** - Relative Area

rd - Destination Registers

**RE** - Relative Error

**REACT** - Rapid Exploration of Approximate Computing Techniques

**REp** - Relative Error Percentage

RISC-V - Reduced Instruction Set Computer V

rm - Rounding Mode

$\mathbf{RP}$  - Relative Power

RP<sub>circuit</sub> - Relative Power Approximate Circuit

$\mathbf{RP_{prog}}$  - Relative Power per Program

rs - Source Registers

SDRAM - Synchronous Dynamic Random Access Memory

$\mathbf{SoC}$  - System-on-chip

$\mathbf{SP}$  - Static Power

**SRAM** - Static Random Access Memory

**TA** - Fully Approximate Circuits

$\mathbf{TP}$  - Total Power Dissipation

$\mathbf{T_{I}}$  - Total of Instructions

$\mathbf{T_{ILAF}}$  - Total ILAF Approximate Instructions

VHDL - Very High Speed Integrated Circuits Language

# Chapter 1

# Introduction

The exponential growth in computing power demand and the limitations imposed by the end of the Dennard scale [16], have challenged designers to find alternative solutions to maintain system performance within limited energy and cost budgets. Precise computing requires high resources to ensure the accuracy of results. However, many applications, such as image processing, data mining, and machine learning, can tolerate a certain degree of inaccuracy in calculations without significantly compromising the quality of the final results.

In this context, approximate computing (AC) emerges as a promising approach to balance the need for performance and energy efficiency in applications that tolerate acceptable error margins. Approximate computing encompasses a range of techniques that vary from the circuit level to the application level, enabling the development of hardware and software that perform calculations with reduced precision but with significant gains in energy consumption and performance [79].

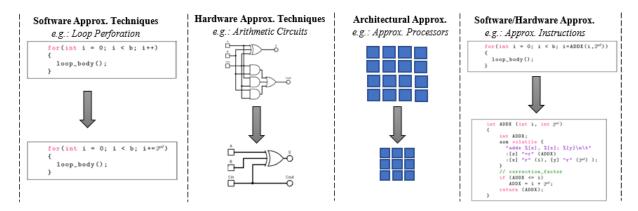

Figure 1.1 presents examples of approximate computing approaches. In software, the Loop Perforation technique modifies the loops increment, reducing runtime. In hardware, approximate circuits minimize the area usage, and potentially, the power consumption, by simplifying the number of logical components. At the architectural level, approximations allow the creation of approximate cores. Software/Hardware approximation techniques can be exemplified combining approximate instructions and software techniques offers performance/power consumption gains.

At the circuit level, several proposals for approximate arithmetic circuits, such as adders, subtractors, multipliers, and dividers [30, 24, 31], have been widely studied. These circuits aim to reduce the circuit's area, energy consumption, and delay time at the cost of lower calculation precision. Most current proposals focus on small-scale circuits with single-bit operations, needing deeper analyses of the behavior of such circuits in real platforms and with larger inputs. Furthermore, when evaluating small circuits, these works do not have the opportunity to analyze the circuit accuracy and physical behavior in the presence of long inputs and outputs or even on a real-world design platform.

Figure 1.1: Examples of approximate computing techniques: software, hardware, architecture, and software/hardware. Source: author.

On the other hand, at the software level, most AC techniques aim to solve specific problems or require intervention from the programmer, who should identify which application parts are susceptible to approximations [53]. AC techniques also target identifying parts of an application that can be approximated, allowing for resource savings while maintaining the application's proper functionality.

One opportunity to advance in approximate computing lies in introducing an additional level of approximation with the combined usage of hardware and software techniques. From this perspective, this thesis presents a set of studies and approaches for exploiting hardware/software approximate techniques. Specifically, this research work has investigated and designed a range of approximate arithmetic circuits to work as building blocks of new instructions. These instructions show their applicability in different software techniques such as loop perforation and approximate mathematical functions. To carry out this research, we have extended a toolchain based on the RISC-V processor architecture [56]. Concerning the research goals, this thesis has the following:

- Explore the impact of approximate computing at different levels of abstraction, focusing on the implications of accuracy, power consumption, and performance;

- Investigate and propose innovative approximate computing techniques at different levels of abstraction (software and hardware);

- Integrate AC techniques into widely adopted platforms, such as the RISC-V architecture, providing an infrastructure for developing approximate systems;

- Investigate the feasibility of approximation techniques in mathematical functions and control structures, such as loops, for applications that require high performance but tolerate controlled errors;

- Analyze the impact of approximate computing techniques in real applications, seeking a balance between efficiency and precision.

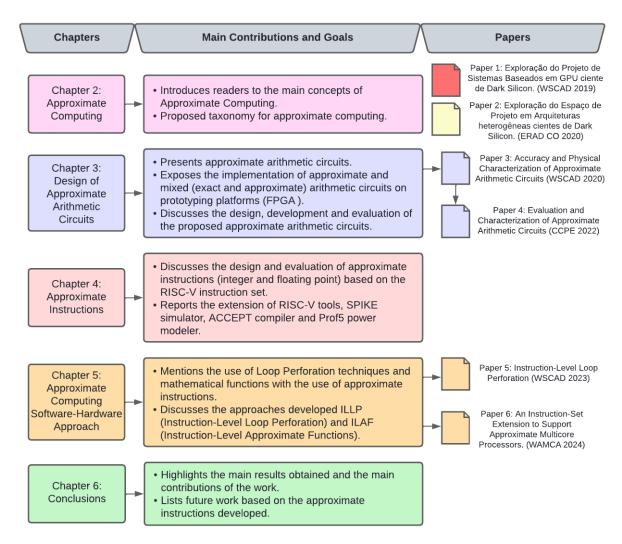

This manuscript is structured as illustrated in Figure 1.2, which presents the published papers as outcomes of each research step. The papers present the physical characterization and evaluation of approximate arithmetic circuits [7, 8], the instruction-level approach to loop perforation [9], and the instruction-level approach to approximate mathematical functions [10]. Other publications carried out along this work present the exploration of dark silicon-aware GPU-based system designs [62] and design space exploration in dark-silicon-aware heterogeneous architectures [6].

Figure 1.2: Overall structural diagram of the thesis chapters. Source: author.

# Chapter 2

# **Approximate Computing**

Approximate computing offers techniques ranging from the circuit level to the application level, providing benefits on energy efficiency, faster runtime, and even circuits' area shrinking. This chapter introduces AC concepts and techniques, classifying them into physical, logical, and architectural levels. This chapter also highlights the need to balance precision and performance when adopting AC techniques.

#### 2.1 Contextualization

Approximate computing is an emerging paradigm that proposes the introduction of insignificant and controlled inaccuracies so that significant savings can be achieved in design metrics such as execution time, design area, and energy efficiency [14]. According to Palem and Lingamneni [49], the first idea of approximate computing was used in approximate signal processing, where approximation was approached to design systems with limited resources in the areas of artificial intelligence and real-time computing. The second idea came from algorithmic noise tolerance, allowing circuits to be unreliable in the first instance but to use algorithmic error control schemes based on system statistics and input and output behavior to fix resulting errors. From these ideas, inaccurate design began to be applied at the physical design level, logical design, and architectural layers. Many computing processes and/or tasks may require little precision in their results. Some applications of machine learning, signal processing, database analysis, computer vision, and natural language processing do not require an exact answer but a "good enough" result for their purpose [2].

AC provides greater freedom to explore the design space, as it allows compromising computational precision to obtain new regions of performance that were not possible in the traditional way. However, the challenge is the difficulty of determining how safe an approach is for a system or application and predicting how it behaves in synergy with other systems participating in the collaboration. Although promising, effective use of

AC requires carefully selecting the parts of the system (circuit, hardware, or software) that can be approximated and the approximation strategies. Inappropriate use of AC may lead to an unacceptable quality loss.

The related research presents different AC metrics, such as minimum acceptable precision, amplitude precision, information precision, average error distance, normalized error distance, error rate, error significance, maximum error, and magnitude, among others [63, 20, 79]. Most metrics compare some output items in the approximate calculation with the exact calculation.

AC presents differs characteristic terminology, such as the term *error*, which indicates that the result with AC from the result without AC, differentiating itself from the meaning of *fail* in which it is commonly used, when referring to the fact that the result did not come out as expected. Another characteristic term is *accuracy*, a crucial concept that refers to the distance between the approximate and exact result (this distance is calculated using error metrics, such as Relative Error). The terms *exact/accurate/non-approximate* refer to an application or result without approximation techniques, generally used as a comparison reference for results with approximate techniques.

#### 2.2 Organization of AC Techniques

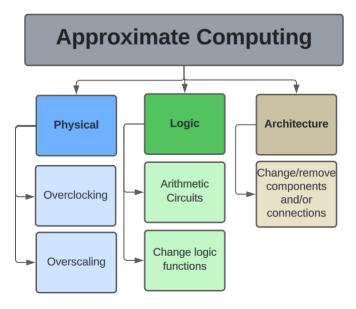

Many research works focus on organizing the set of AC techniques into specific categories. Palem and Lingamneni [49] divide AC into Physical, Logical, and Architecture (Figure 2.1). The physical category concerns methods that change the operating conditions of a circuit, such as voltage and energy consumption. At the logical category, methods to change the logical functions of a computational block, such as an adder or multiplier, are applied to reduce the complexity of the circuit, area, or energy consumption. Finally, the architectural category refers to methods that somehow change the architecture of a system, removing components and/or connections to save resources.

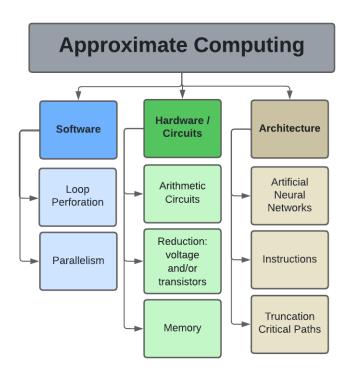

Shafique et al. [63] classify AC approaches into Software, Hardware/Circuits, and Architecture (Figure 2.2). The software category approach encompasses manual and automatic annotation techniques to skip code snippets and parallels and exchange precise modules for approximate ones. Despite recognizing the potential to use multiple techniques simultaneously at different categories, the work maintains its classification into only three main categories. Approximations at the hardware/circuit category include designing approximate versions of logic circuits using algorithms or designing arithmetic datapaths with approximate adders or multipliers, supply voltage reduction techniques, minimize the number of transistors, and reduction in memory units. Approximations at the architectural category can be made with complex algorithms using Artificial Neural Networks (ANNs) to identify critical neurons with approximate instructions and truncation of critical paths.

Leon et al. [32] proposed a classification of AC approaches divided into software,

Figure 2.1: Classification of AC proposed by Palem and Lingamneni. Source: [49].

Figure 2.2: Classification of AC techniques proposed by Shafique et al. Source: [63].

hardware, and architecture, considering the techniques of approximate programming languages, loop perforation, and memory access skipping as approximate software methods. Approximate hardware comprises arithmetic circuits (addition, multiplication, and division) and approximate synthesis (automatic approach to generating inexact cir-

cuits). Approximate architecture are approximate processors and approximate data storage (Figure 2.3). Xu et. al [79] use the same approach to organize AC techniques but add Instruction Set Architecture (ISA) extensions to the architecture category.

Figure 2.3: Classification of AC techniques proposed by Vasileios et al. and Xu et al. Source: [32, 79].

The scientific work proposing taxonomies for AC, classifies approximate computation reflecting the technological developments of their time and specific contexts [42, 27, 2]. However, as one may notice, the authors adopt the same standard categories (software, hardware, architecture) to organize the techniques. Classifications are expected to cover as many techniques as possible in the least general way; after all, classifying with hardware and software is already a common classification. The classifications should evolve as new challenges and solutions emerge, reflecting the diversity of applications and the interdisciplinary nature of approximate computing. For example, the AC approaches presented in [59, 21, 73] whose proposals simultaneously employ multiple techniques. Regarding new AC techniques that may find difficult to fit into the previous classifications, Figure 2.4 presents a new extended taxonomy for AC techniques. The new techniques are represented in double borders. The novelty is on the Software/Hardware category, which covers software techniques relying on approximate hardware.

The Loop Perforation (LP) technique is widely used in AC, since any modification in the loop increment already makes it approximate. Several software techniques are employed for this purpose; however, the use of hardware techniques to complement LP is still in the development phase. Catelan et al. [9], who exploit approximate instructions

in hardware to modify the LP increment. Similarly, approximate mathematical functions have several software-based approximation techniques, but also allow the replacement of exact instructions by approximate instructions in hardware, as demonstrated by Catelan et al. [10].

Figure 2.4: Proposed taxonomy for approximate computing. Source: author.

#### 2.3 Software Support for Approximate Computing

The objective of software approximate computing techniques is to improve programs' runtime and/or energy consumption. Typical software techniques are approximated libraries/frameworks, compiler extensions, precision tuning tools, runtime systems, and language annotations [32].

REACT (Rapid Exploration of Approximate Computing Techniques) [77] is a modeling framework that allows researchers to rapidly evaluate approximate computing techniques for achieving energy efficiency and modeling through user-initiated error injection. Techniques that REACT can evaluate include data approximation, which introduces controlled errors to reduce energy consumption; operations approximation, which uses simplified arithmetic operations; and circuit approximation, where deliberate faults are introduced to reduce area or energy consumption; control approximation, which modifies the program control flow to avoid complex computations; and error modeling, which allows controlled injection of errors to study the impact of approximations on

the quality of results. REACT employs a custom linear energy model to estimate energy savings. It allows accurate and rapid exploration of the energy-quality trade-off space of approximate computing. The paper lists eight approximate computing techniques, such as DRAM Refresh Rate, Neural Acceleration, and Precision Scaling. The tests were performed using applications with varying AC techniques. The results show an average error of 0.87%, ranging from 0.31% to 1.38%, depending on the AC technique and the application under analysis.

FlexJava [51] features a small set of extensions that reduce annotation effort for approximate programming, allowing programmers to annotate outputs that exhibit approximation tolerance. Programmers need to manually write down all approximate variables, statements, and safe operations to approximate. The FlexJava compiler, equipped with an approximation safety analysis, automatically infers operations and data that affect these outputs and selectively marks them as approximations, giving safety guarantees. The results achieved energy reduction when exchanging precise computation for approximate computation. FlexJava results are based on comparisons to EnerJ [59]. FlexJava reduced the number of annotations between 2 and 17× and a reduction in annotation time between 6 and 12×, keeping the same level of energy savings.

AppSyn [4] is a synthesizer program that can take specific input, an input-output set, or a complete implementation reference. AppSyn searches among the implementations to find a program that meets a given specification. The programmer only needs to provide a reference and a desired precision value. The synthesizer will try to find an approximate implementation that satisfies the given limits. The synthesizer also validates whether the approximate program result is more efficient than the reference. The output is the approximate implementation, and a table with speedup results.

ACCEPT [58] compiler introduces specific annotations to show the programmer which code regions are more suitable for approximation and which techniques would be most promising. The ACCEPT offers a set of techniques to users interested in applying approximations in a program: loop perforation, loop parallelization, neural acceleration, and approximate functions. The compiler evaluates the approximation techniques in the code and presents performance and accuracy results, thus allowing the programmer to analyze the impact of the approximations.

Loop Perforation (LP) is an AC software technique that has been gaining appreciation among designers because it is simple, general purpose, and is widely applicable. LP consists of skipping loop iterations to reduce computational workload and gain performance. A simple change in the loop step variable is enough to change its performance, but manually changing one or more loops of an application sometimes becomes more costly than the loop execution itself. ACCEPT compiler automatizes the process to find suitable loops for perforation. The tool considers only canonical loops fitted for perforation, which have a precise body without early exits and conditionals. The ACCEPT divides the loop into three blocks: the header, the body, and the latch. Loop calculations are performed inside the body, and the header and latch are responsible for changing condition variables and checking jump conditions. Other techniques are also applied to

find loops for perforation, such as: perforation space exploration algorithm [64], selective dynamic [34], time redundancy [44], polyhedral compilation [3], Linear Interpolation (LI), and LP with Nearest Neighbor (NN) [57].

Most software techniques found in the literature seek to find code sections that can be automatically [59, 58] or manually [4] carried out inserting approximate code, variables, loops, and functions. There are also benchmarks capable of approximate computing to ensure fairer and more reproducible comparisons. AxBench [81] has a representative set of applications for a fair evaluation of different approximation techniques. It contains applications for Central Process Unit (CPU) (C/C++), Graphics Processing Unit (GPU) (CUDA), and hardware (Verilog). Table 2.1 presents 21 applications, platforms, domains, and metrics from AxBench.

| Table 2.1: Applications, platforms, domains, and metrics of AxBench. Source: [81] | Table 2.1: App | olications, pla | tforms, domains. | , and metrics | of AxBenc | h. Source: | [81]. |

|-----------------------------------------------------------------------------------|----------------|-----------------|------------------|---------------|-----------|------------|-------|

|-----------------------------------------------------------------------------------|----------------|-----------------|------------------|---------------|-----------|------------|-------|

| Applications   | Platforms          | Domains                  | Metrics                |  |  |

|----------------|--------------------|--------------------------|------------------------|--|--|

| binarization   | GPU                | Image Processing         | Image Difference       |  |  |

| blackscholes   | CPU, GPU           | Finance                  | Average Relative Error |  |  |

| brent-kung     | Hardware           | Computational Arithmetic | Average Relative Error |  |  |

| cannel         | CPU                | Computational Arithmetic | Average Relative Error |  |  |

| convolution    | GPU                | Machine Learning         | Average Relative Error |  |  |

| fastwalsh      | GPU                | Signal Processing        | Image Difference       |  |  |

| fft            | CPU                | Signal Processing        | Average Relative Error |  |  |

| fir            | Hardware           | Signal Processing        | Average Relative Error |  |  |

| forwardk2j     | CPU, Hardware      | Robotics                 | Average Relative Error |  |  |

| inversek2j     | CPU, GPU, Hardware | Robotics                 | Average Relative Error |  |  |

| jmeint         | CPU, GPU           | Games 3D                 | Loss Rate              |  |  |

| jpeg           | CPU                | Image Processing         | Image Difference       |  |  |

| kmeans         | CPU, Hardware      | Machine Learning         | Image Difference       |  |  |

| kogge-stone    | Hardware           | Computational Arithmetic | Average Relative Error |  |  |

| laplacian      | GPU                | Image Processing         | Image Difference       |  |  |

| meanfilter     | GPU                | Machine Vision           | Image Difference       |  |  |

| neural network | Hardware           | Machine Learning         | Average Relative Error |  |  |

| newton-raph    | GPU                | Numerical Analysis       | Average Relative Error |  |  |

| sobel          | CPU, GPU, Hardware | Image Processing         | Image Difference       |  |  |

| srad           | GPU                | Medical Images           | Image Difference       |  |  |

| wallace-tree   | Hardware           | Computational Arithmetic | Average Relative Error |  |  |

### 2.4 Hardware Support for Approximate Computing

One of the AC hardware techniques consists of modifying logical functions to reduce the circuits' complexity and thus reduce area and energy consumption. It is essential to highlight that errors will be introduced into the circuit when modifying logical functions. However, these errors occur in just a few combinations, and the designer considers reducing complexity or energy consumption favorable. In that case, these circuits will be advantageous for approximate applications [74].

Various works propose different techniques (voltage over-scaling, speculative carry select addition, and memristor) for the development of approximate adders [38, 83, 43, 82, 36, 33, 18]. The commonly used technique is circuit minimization, which reduces the

number of logical components in the circuit. Gupta et al. [26] presented an Approximate Mirror Adder (AMA), which, with the removal of transistors and the insertion of minimal errors in the truth table, derives four different circuits for an approximate Full Adder (FA): AMA1, AMA2, AMA3, and AMA4. Compared to other approximate adders, the Inexact Adder Cells (InXA) [1] have fewer transistors on their three terminals, thus occupying a smaller area, in the three designed models, InXA1, InXA2, and InXA3. The Approximate XOR/XNOR-based Adder (AXA) [80] is based on exact adders with XOR and XNOR gates, with a reduction in the number of transistors and the production of three new approximate adders (AXA1, AXA2, and AXA3).

Table 2.2 shows the number of transistors and the number of errors of AXA, AMA, and InXA adders. Note that AXA2, InXA1, and InXA3 adders have the same number of transistors; however, the number of errors is significantly different.

Table 2.2: Comparison among AXA, AMA, and InXA adders. Source: [80, 67].

| Adder | Number of Transistors | Number of errors - SUM |

|-------|-----------------------|------------------------|

| AMA1  | 16                    | 2                      |

| AMA2  | 14                    | 2                      |

| AMA3  | 11                    | 3                      |

| AXA1  | 8                     | 4                      |

| AXA2  | 6                     | 4                      |

| AXA3  | 8                     | 2                      |

| InXA1 | 6                     | 0                      |

| InXA3 | 6                     | 2                      |

Approximate subtractor circuits also use the circuit minimization technique, introducing controlled errors into the truth table and obtaining the logical expression through the Karnaugh Map. Examples of such circuits are the Approximate Subtractor Cell (AXSC) [12] and Approximate Subtractor (APSC) [24] subtractors. The AXSC presents three derivations of approximate subtractors, with the insertion of errors varying between the SUM and Cout outputs for 2 to 4 errors. APSC has four subtractor derivations, with the insertion of 1 error only in the SUM output. Table 2.3 presents the number of errors inserted in each subtractor and the area ( $\mu m^2$ ), using a 45nm transistor. It is noted that the AXSC2 subtractor presents the largest insertion of errors in its outputs, with the smallest area size. The APSC4 subtractor only presents one error in its output, and the area is just one unit larger than that of the AXSC2.

Table 2.3: Comparison between AXSC and APSC subtractor. Source: [24].

| Subtractor | Number of errors | Area $(\mu m^2)$ |

|------------|------------------|------------------|

| AXSC1      | 2                | 16               |

| AXSC2      | 4                | 8                |

| AXSC3      | 2                | 14               |

| APSC4      | 1                | 9                |

| APSC5      | 1                | 15               |

| APSC6      | 1                | 19               |

| APSC7      | 1                | 17               |

In multipliers, the insertion of errors in the truth table is also viable. Kulkarni

et al. [31] presented a conversion of a precise  $2 \times 2$  multiplier to an approximate  $2 \times 2$  multiplier. A single entry in the multiplier truth table was modified. The change reduced the number of logic gates required to implement the multiplier. The proposed approximate multiplier presented an average energy saving between 31.78% and 45.4%, with an average error variation between 1.39% and 3.35%. The average relative error increases with the number of operand bits but saturates between 3.3% and 3.35%.

Another technique used for approximate arithmetic circuits is to replace part of the operation hardware with approximate components. Gorantla and Deepa [24] replaced the subtraction hardware in the divider circuit with the approximate subtractors (APSC), thus obtaining four types of approximate dividers (APDr4-APDr7). These dividers showed low power consumption (APDr4 = 71%), lower delay (APDr6 = 40%) and smaller area (APDr4 = 29%) compared to the exact divider.

EvoApprox8b [45] is an 8-bit approximate adder designed to improve speed and power consumption efficiency, especially in embedded systems and mobile devices. Instead of providing exact results, EvoApprox8b uses hardware approximation techniques to simplify addition operations, which reduces the number of transistors and signal propagation time. This is achieved by modifying the digital circuit architecture, including reducing the complexity of logic gates and eliminating intermediate operations. This approach results in an adder that sacrifices some accuracy in favor of faster performance and lower power consumption. By employing approximation directly at the hardware level, EvoApprox8b provides an efficient solution for applications where absolute accuracy is not critical, but system efficiency is paramount. EvoApprox8b is a benchmark for circuit approximation methods, having a library with 430 approximate adders and 471 approximate multipliers, both 8 bits, with models in Verilog, Matlab, and C of all circuits approximate, in addition to presenting seven different error metrics, area, delay, and power. The use of EvoApprox8b allows the integration of hardware and software design circuits.

# 2.5 Software/Hardware Support for Approximate Computing

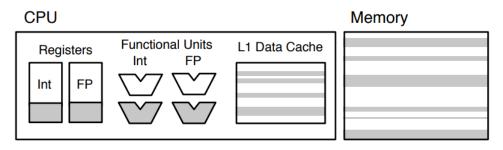

The category of software/hardware support for AC is comprised of frameworks, such as EnerJ [59], RISK-5 [21], and QUORA [73], which have software for control approximation depending on approximate hardware, such as SRAM, DRAM, and operations units (with integers and floating point numbers).

The EnerJ simulator is a Java extension that allows the addition of approximate data types. The model proposes using qualifiers to declare data that can be subject to approximate calculation. EnerJ automatically maps approximate variables to low-power storage and utilizes low-power operations. Figure 2.5 presents the hardware model assumed in the EnerJ system, where the shaded areas indicate approximate components.

The SRAM cells in the register and data caches reduce the supply voltage. The floating point unit performs approximation using reduced mantissa. The reduction in the update rate makes the main memory (DRAM) approximate. This allows the programmer to explicitly control how information flows from approximate data to precise data.

Figure 2.5: EnerJ hardware model. Source: [59].

RISK-5 [21] is an extension of RISC-V ISA for approximate hardware unit control. RISK-5 extends the RISC-V architecture, implementing control mechanisms combining several approximation techniques. The approximate hardware resources are informed to the software, that in turn, has control of what and how much approximation will be used in an application. This control can range from turning approximate hardware on/off to configure allowable error levels and probabilistic error configuration operating parameters, such as the refresh rate for approximate SDRAM. Approximations can be configured dynamically, allowing for simplified design space exploration. Figure 2.6 provides a visual representation of the RISK-5 hardware. The key component is the status register, which is responsible for the approximation control of each unit.

Figure 2.6: RISK-5 hardware schematic. Source: [21].

Quality programmable vector processors for approximate computing (QUORA) [73] is a programmable processor that expresses its tolerance for AC at the hardware-software

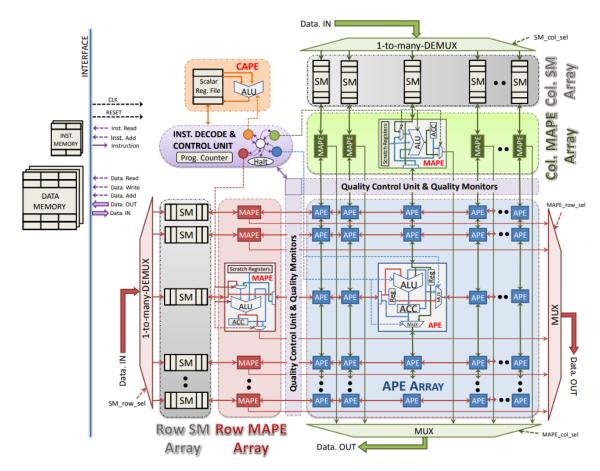

interface (HW/SW), having as its main components a quality programmable ISA (QP -ISA) and a microarchitecture (QP-uArch). QUORA features precision scaling-based hardware mechanisms with error monitoring and compensation to facilitate configurable quality execution across these processing elements and demonstrate significant energy benefits. The HW/SW interface allows approximate instructions to be identified and specifies the amount of error each instruction can tolerate during its execution. Figure 2.7 presents the QUORA microarchitecture. The QUORA design has three hierarchy levels: APE - Approximate Processing Elements, MAPE - Mixed Accuracy Processing Elements, and CAPE - Completely Accurate Processing Element. These levels provide different trade-offs between power and quality, and the hardware mechanisms are based on precision scaling with monitoring and error compensation.

Figure 2.7: QUORA microarchitecture. Source: [73].

# 2.6 Architectural Support for Approximate Computing

This section presents the architectural support for AC regarding strategies using approximate memories. When an application can tolerate occasional errors in some data, approximate storage is used, and data recovery errors may occur. In either case, software must determine which data can tolerate errors and which needs accuracy. There are several propositions for adopting approximate memories [39]. The Unreliable Retention technique is the most used. This technique is restricted to DRAM and consists of updating at longer intervals than the maximum guaranteed retention of the cells. As a result, the bits that store 1 can lose their stored value due to capacitor discharge.

Sampson et al. [60] propose two approximated memory techniques. The first uses multi-level cells (MLC - Multi-Level Cell Model) to allow greater density or better performance, considering the cost of imprecise errors caused in data recovery. The other technique uses of faulty bit blocks to store approximate data. MLC storage blocks that have faults. When the first uncorrectable block fails, the memory will issue an interrupt and indicate the failed block, which will be used as a temporary storage block. The authors conclude that approximate storage helps mitigate the disadvantages of solid-state systems and non-volatile memories, as there is no significant compromise in storage quality for write acceleration and lifetime extension criteria.

Another approach of approximate memories was demonstrated in [37]. The discrete cosine transform (DCT) was applied to a dimension between the cache and main memory to reduce memory traffic while maintaining acceptable quality degradation using natural sampled data such as sound, sensor data, and images. The DCT performs an orthogonal transformation that preserves energy, and its transformation matrix is orthonormal, thus allowing an approximate DCT matrix to be written. The approximate DCT was used in an approximate memory based on lossy compression, performing transformations of memory blocks. As a result, the authors point out that a DCT of approximately 8 points has better compression performance for approximate memory than a DCT of 16 points.

#### 2.7 Final Remarks

This chapter presented an overview of approximate computing, demonstrating its main techniques and applications in both software and hardware levels. AC is still an underexploited area with diverse research possibilities, given that most existing work is related to specific applications, a limited set of bits, or requires much knowledge from the programmer. Regarding approximate circuits, there is great potential for exploiting mixed exact/approximate circuits that provide a balance between precision and energy efficiency. Another promising field is the development of approximate instruction sets combining integer and approximate floating point instructions, which would allow the

execution of complex mathematical operations with less consumption of computational resources. The diversity of AC techniques reflects the interdisciplinary nature of this subject, requiring a constant evolution of classifications and approaches.

# Chapter 3

# Design of Approximate Arithmetic Circuits

This chapter studies approximate arithmetic circuits. We discuss the design, development, and evaluation of approximate arithmetic circuits developed as part of this thesis. The chapter also presents experiments and results of prototyping those circuits on Field-Programmable Gate Array (FPGA) platforms. The results present the trade-offs between accuracy, resource usage, and energy efficiency.

#### 3.1 Contextualization

The difficulty of accommodating more cores in constrained power budgets threatens even the multicore scaling paradigm. Thus, designers seek new computing sources to deliver better performance with power and cost constraints. The workloads that drive computing demand have also fundamentally changed across the computing spectrum, from mobile devices to the cloud. Such workloads exhibit intrinsic resilience to approximations and an ability to produce acceptable outputs even when some of their calculations are inaccurate [72].

Some authors [27, 49] indicate that AC techniques can be applied at the logical level that cover methods to approximate logic functions in digital circuits. There is a diversity of proposals for approximate circuits [30, 24, 31, 13], mainly for approximate adders, subtractors, multipliers, and dividers. Most of these studies present circuits with just 1-bit, showing details such as error placement, area usage, power, and delay. When evaluating small circuits, these works need more opportunities to analyze how circuit accuracy and physical behavior will perform in the presence of larger inputs and outputs and even in a real-world design platform.

The following sections will present an analysis of the behavior of a wide range of

precision-controlled approximate arithmetic circuits. An evaluation of those circuits on flexible prototyping platforms, such as FPGAs, is also presented and discussed.

#### 3.2 Approximate Arithmetic Circuit Designs

There are many proposals of approximate circuit designs [26, 80, 1, 30, 47, 24, 13], mainly focusing on approximate arithmetic circuits such as adders, subtractors, multipliers, and dividers. Some studies present circuits with just 1-bit, evaluating their features regarding error positioning, area usage, power, and delay.

Most research presents only a single circuit to control accuracy. For example, Gorantla and Deepa [24] present four types of subtractors (APSC4-APSC7), where the difference between them is only the position where the error was inserted in the truth table. Although the APSC circuit is visibly larger than the exact subtractor, there are considerable power gains. The APSC4, with 90nm transistors, achieves a power of 891nW compared to the 3475nW of the exact subtractor [24].

Approximate subtractors AXSC1, AXSC2, and AXSC3 are based on XOR and XNOR cells with transistor reduction in each cell. Chen et al. [13] indicated that the precision of the Cout output is more important than the S output. Cout remains unchanged in AXSC1 and AXSC3, and a combination of the outputs S and Cout, aiming to reduce the delay, is proposed in AXSC2 and AXSC3. AXSC approximate subtractors have an absolute error distance between 2 and 4. The logic circuits of the AXSC subtractors are smaller than the exact subtractor, which is consistent with the reduction in the size of the area, with 180nm transistors of the AXSC2 of  $50\mu m^2$  compared to the exact subtractor that has  $90\mu m^2$  of area [24].

The approximate adder designs of AMA type (Approximate Mirror Adder - AMA) [26] is based on the Mirror Adder. In an AMA design, the transistors of the conventional circuit were removed one by one, always ensuring that for any combination of the inputs A, B and Cin would not result in a short circuit or open circuit. A few errors in the truth table were inserted and a set of approximate adder circuits were derived (AMA1, AMA2, AMA3, and AMA4). However, taking into account the size of the logical expression, only the approximate adders AMA1, AMA3, and AMA4 were used for the tests. Compared to the full adder that has an area of  $40.66\mu m^2$ , the AMA3 and AMA4 adders have an area, respectively, of  $22.56\mu m^2$  and  $23.91\mu m^2$  [26].

The AXA adder (Approximate XOR/XNOR - based Adder) [80] was designed based on the transistor removal technique. The complete AXA1 adder is an exact adder with XOR gates and its implementation uses 8 transistors. The AXA2 adder is based on XNOR ports requiring 6 transistors. The AXA3 adder was based on the AXA2 adder with two more transistors for better accuracy. The three models were evaluated in this work. Concerning the exact adder, the AXA2 improves 65.45% in static power [80].

The approximate InXA1, InXA2, and InXA3 adder models [1] were developed with inexact adder cells with less circuit complexity compared to other approximate circuits found in the area (AMA, AXA, LOA, and ESA). The InXA1 adder has an approximate design on the *Cout* output. InXA2 and InXA3 have approximate designs on the *S* output. InXA1 and InXA3 were evaluated in this work. Analyzing delay, energy dissipation, and the energy-delay-product (EDP), the InXA1 and InXA2 adders outperform the AMAs and AXAs adders in all metrics; however, the InXA3, despite dissipating less energy, incurs a higher amount of delay [1].

Table 3.1 presents the logical expressions of the approximate adder circuits. The S output is different among the circuits once it is focused on approximate designs. Regarding the Cout output, one may also observe that the AXA1 adder has a more complex logic; AMA1, AMA3, AXA2, and AXA3 have the same expression in the Cout output.

Table 3.1: Logical expressions for approximate adders. Source: author.

| Circuits | Output | Logical Expression                                          |

|----------|--------|-------------------------------------------------------------|

| AMA1     | S      | $\overline{A}.\overline{B}.Cin + A.B.Cin$                   |

|          | Cout   | A.Cin + B                                                   |

| AMA3     | S      | $\overline{(A.Cin+B)}$                                      |

|          | Cout   | A.Cin + B                                                   |

| AMA4     | S      | $\overline{A}.Cin + B.Cin$                                  |

|          | Cout   | A                                                           |

| AXA1     | S      | Cin                                                         |

|          | Cout   | $\overline{((A \oplus B).Cin + \overline{A}.\overline{B})}$ |

| Circuits | Output | Logical Expression            |

|----------|--------|-------------------------------|

| AXA2     | S      | $\overline{(A \oplus B)}$     |

|          | Cout   | $(A \oplus B).Cin + A.B$      |

| AXA3     | S      | $\overline{(A \oplus B)}.Cin$ |

|          | Cout   | $(A \oplus B).Cin + A.B$      |

| InXA1    | S      | $A \oplus B \oplus Cin$       |

|          | Cout   | Cin                           |

| InXA3    | S      | $\overline{Cout}$             |

|          | Cout   | $(A \oplus B).Cin + A.B$      |

Approximate subtractors APSC4-APSC7 have a single error inserted in output S and output Cout is the same for all subtractors, so the absolute error distance is 1. Approximate subtractors AXSC1-AXSC3 have the same Cout output in AXSC1 and AXSC3, and the same as the S output in AXSC2. Table 3.2 shows the logical expressions of the approximate subtractor circuits.

Table 3.2: Logical expressions for the approximate subtractors. Source: author.

| Circuits | Logical Expression                                                          |

|----------|-----------------------------------------------------------------------------|

| APSC4    | $\overline{A}.B + B.Cin + \overline{A}.Cin + A.\overline{B}.\overline{Cin}$ |

| APSC5    | $A.\overline{B} + \overline{B}.Cin + \overline{A}.B.\overline{Cin} + A.Cin$ |

| APSC6    | $A.B.Cin + \overline{A}.B.\overline{Cin} + \overline{A}.\overline{B}.Cin$   |

| APSC7    | $A.\overline{B}.\overline{Cin} + \overline{A}.\overline{B}.Cin + A.B.Cin$   |

| Circuits | Logical Expression      |

|----------|-------------------------|

| AXSC1    | $A \oplus B + Cin$      |

| AXSC2    | $A \oplus B \oplus Cin$ |

| AXSC3    | Cout                    |

The subtractors APSC4-APSC7, AXSC1, and AXSC3 designs have the same logical expression for the Cout output:

$$Cout = \overline{(A \oplus B)}.Cin + \overline{A}.B$$

Kulkarni [31] presents the conversion of a precise  $2 \times 2$  multiplier to an approximate  $2 \times 2$  multiplier. A single entry of the multiplier truth table was modified for the conversion, as highlighted (bold) in Table 3.3. The modified entry in the truth table refers to the multiplication of  $11_2$  by  $11_2$ , whose precise result is  $1001_2$ , and whose approximate result equals  $111_2$ . This change reduced the number of logic gates required to implement the multiplier. The approximate multiplier showed an average energy saving between 31.78% and 45.4%, with the average error variation of 1.39% and 3.35%. The average relative error increases according to the number of operand bits; however, it saturates between 3.3% and 3.35%.

| Table 3.3: <i>A</i> | Approximate | $2 \times 2$ | multiplier | truth table. | Source: | [31] |  |

|---------------------|-------------|--------------|------------|--------------|---------|------|--|

|                     |             |              |            |              |         |      |  |

|    | Inp        | out |    | Output |      |      |  |

|----|------------|-----|----|--------|------|------|--|

| A1 | <b>A</b> 0 | B1  | B0 | Out2   | Out1 | Out0 |  |

| 0  | 0          | 0   | 0  | 0      | 0    | 0    |  |

| 0  | 0          | 0   | 1  | 0      | 0    | 0    |  |

| 0  | 0          | 1   | 0  | 0      | 0    | 0    |  |

| 0  | 0          | 1   | 1  | 0      | 0    | 0    |  |

| 0  | 1          | 0   | 0  | 0      | 0    | 0    |  |

| 0  | 1          | 0   | 1  | 0      | 0    | 1    |  |

| 0  | 1          | 1   | 0  | 0      | 1    | 0    |  |

| 0  | 1          | 1   | 1  | 0      | 1    | 1    |  |

| 1  | 0          | 0   | 0  | 0      | 0    | 0    |  |

| 1  | 0          | 0   | 1  | 0      | 1    | 0    |  |

| 1  | 0          | 1   | 0  | 1      | 0    | 0    |  |

| 1  | 0          | 1   | 1  | 1      | 1    | 0    |  |

| 1  | 1          | 0   | 0  | 0      | 0    | 0    |  |

| 1  | 1          | 0   | 1  | 0      | 1    | 1    |  |

| 1  | 1          | 1   | 0  | 1      | 1    | 0    |  |

| 1  | 1          | 1   | 1  | 1      | 1    | 1    |  |

The division process includes subtraction, shifting, and comparison. Gorantla and Deepa [24] replaced the subtraction hardware in the divider circuit with the approximate subtractors (APSCs) they proposed, thus obtaining four types of approximate dividers (APDr4-APDr7). Validation of approximate dividers was implemented in Verilog HDL using transistor libraries with 180nm, 90nm, and 45nm technologies in the Cadence RTL compiler. The approximate dividers showed low power consumption (APDr4 = 71%), shorter delay (APDr6 = 40%), and smaller area (APDr4 = 29%) compared to the exact divider.

# 3.3 Experimental Setup, Results, and Discussion

We performed experiments to evaluate precise, approximate, and mixed arithmetic circuits. The approximate arithmetic circuits were built with a reconfigurable FPGA platform and were organized into 4 circuit types: adders, subtractors, multipliers, and dividers with different bit widths (8-, 16-, 32-, and 64-bits). The analyzed circuits were compared in accuracy, area usage, and power dissipation metrics.

The experiments were performed considering precise circuits, approximate circuits,

and mixed circuits (precise and approximate). The mixed circuits were designed so that the bit width design was divided into first and second halves. The first half (least significant bits) comprised precise circuits and the second half (most significant bits) of approximate circuits. The results of mixed circuits will be represented with a capital "M" as the first letter.

The experiments used 8 approximate adder circuits and 7 approximate subtractor circuits. The design of the approximate multiplier circuits was built based on the approximate adders as building blocks. Approximate divider circuits were developed based on the approximate subtractors. The complete experimentation with the approximate arithmetic circuits, with detailed information about the procedures used, tools, data for circuit evaluation, complete tables with results, and metrics used, can be found in the paper [7, 8]. This section will present the main results with their respective analyses and discussions.

All circuits were designed in VHDL, synthesized on the Cyclone IV GX FPGA with the ALTERA Quartus II Web Edition 13.1 IDE tool. Simulation scripts and testbenches were simulated using the Altera-ModelSim 10 tool. The area usage results come from the number of FPGA logic elements used by the circuit design. The total power dissipated was obtained by the PowerPlay Power Analyzer tool. PowerPlay estimates the design power dissipation (PD) by the sum of static power (SP), dynamic power (DP), and I/O power (IOP).

Figure 3.1 presents the VHDL code of the exact 1-bit adder. In lines 16 and 17, there are the logical output expressions Cout and S. Figure 3.2 presents the VHDL code of the approximate adder with the 1-bit InXA3, identified by the entity  $Adder\_InXA3\_1$ , where "1" is the number of bits in the adder in question. Lines 16 to 21 express the logical output functions Cout and S. To change the type of approximate adder, simply replace the code section of these lines with the logical expressions of the adder outputs—desired approximate value, as well as the entity's name<sup>1</sup>.

Figure 3.3 shows the design of the mixed approximate adder with 2 bits InXA3, identified by the entity  $Adder\_M\_InXA3\_2$ , where "2" refers to 2-bits. Note that the component  $Adder\_InXA3\_1$  (line 17) represents the approximate adder and the component  $Adder\_Accuracy\_1$  (line 22) is the exact adder. Both make up the structure of the mixed adder. FA0 (line 28) represents the least significant bit and is composed of the exact adder, while FA1 (line 30) is the most significant bit and is composed of the InXA3 approximate adder. To increase the number of bits in the mixed adder, increase the number of FA. Similarly, the operation of the other proposed approximate arithmetic circuits works.

The accuracy metric is based on the relative error percentage (REp =  $1 - \frac{AO}{EO}$ ) of the approximate circuits over the accurate circuits. To calculate the relative error percentage, we developed a testbench performing a line-by-line comparison between the

<sup>&</sup>lt;sup>1</sup>Arithmetic circuits from 1 to 32 bits are available at: https://github.com/danielacatelan/Circuits-Approximate

```

library IEEE;

1

use IEEE.STD_LOGIC_1164.all;

2

entity Adder_Accuracy_1 is

3

port

(

8

cin: in std_logic;

a: in std_logic;

b: in std_logic;

cout: out std_logic;

9

s: out std_logic

10

);

11

end Adder_Accuracy_1;

12

13

architecture Adder1Bit of Adder_Accuracy_1 is

14

begin

15

cout <= (a and b) or (a and cin) or (b and cin);</pre>

16

s <= a xor b xor cin;

17

end Adder1Bit;

18

```

Figure 3.1: 1-bit accuracy adder in VHDL code. Source: author.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

2

entity Adder_InXA3_1 is

port

cin: in std_logic;

a: in std_logic;

b: in std_logic;

cout: out std_logic;

s: out std_logic

10

11

end Adder_InXA3_1;

12

architecture Adder1Bit of Adder_InXA3_1 is

13

signal c1, c2, c3 : std_logic;

14

begin

c1 <= a xor b;

16

c2 \le a and b;

17

c3 <= c1 and cin;

18

19

cout <= c2 or c3;

s <= not (c2 or c3);

21

end Adder1Bit;

22

```

Figure 3.2: 1-bit approximate adder InXA3 in VHDL code. Source: author.

```

library IEEE;

1

use IEEE.STD_LOGIC_1164.all;

2

3

entity Adder_M_InXA3_2 is

4

port(

5

a: in std_logic_vector(1 downto 0);

b: in std_logic_vector(1 downto 0);

cin: in std_logic;

cout: out std_logic;

9

s: out std_logic_vector(1 downto 0)

10

);

11

end Adder_M_InXA3_2;

12

13

architecture Adder2Bits of Adder_M_InXA3_2 is

14

signal c: std_logic_vector(1 downto 0);

15

16

component Adder_InXA3_1

17

port( cin, a, b : in std_logic;

18

cout, s : out std_logic);

19

end component;

20

21

component Adder_Accuracy_1

port( cin, a, b : in std_logic;

23

cout, s : out std_logic);

^{24}

end component;

25

26

begin

27

FAO: Adder_Accuracy_1

^{28}

port map (cin=>cin, a=>a(0), b=>b(0), s=>s(0), cout=>c(0));

29

FA1 : Adder_InXA3_1

30

port map (cin=>c(0), a=>a(1), b=>b(1), s=>s(1), cout=>cout);

31

end Adder2Bits;

32

```

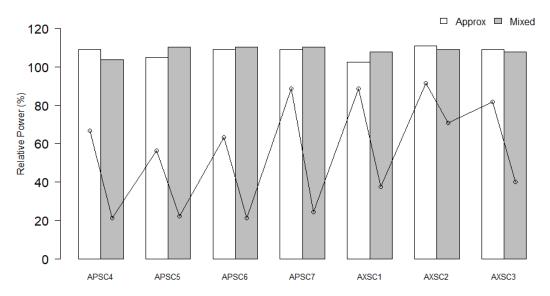

Figure 3.3: 2-bit mixed circuit in VHDL code. Source: author.